On the face of it, computing Z should be no worse than a carry-chain problem, and indeed the inputs to the Z function arrive earliest from the LSB and latest from the MSB, so Z might only need to be a gate-delay behind C. (I say this, knowing that computing Z often does seem to be a time-consuming thing. So I'm interested in why the difference between theory and common practice.)

That makes sense. (Or is it concurrent with C? The carry chain requires an additional gate after the MSB of the result, no?)

I wonder if there is any way to optimize the V flag. It requires the MSB of the result IIRC (which admittedly still emerges from the adder before the final carry. So there is that).

Actually, using a carry look ahead circuitry you can get the C flag at least two gate delays ahead of the result [I mean that we get C before the result, I'm having some use of English trouble with the word 'ahead']. Also you can get the V flag concurrently with the result.

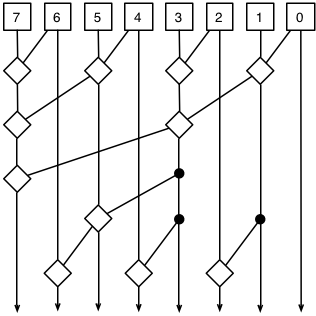

To illustrate it, you can Look at this Logisim Model of my "ALUCore"

https://github.com/John-Lluch/CPU74/blo ... LUCore.png. This is no less and no more than the Dieter multiplexed ALU

http://www.6502.org/users/dieter/a2/a2_1.htm with two levels of carry-lookahead, as seen for the 74xx181 / 74xx182 combinations

http://www.6502.org/users/dieter/a7/a7_3.htm, with the difference that the carry look ahead goes up to Cn+4 instead of only to Cn+3

- The C flag is generated from the second level carry-lookahead circuit, it is shown on the top right of the drawing. Forget about the "SHR Cy" ic for now, and think that the Carry bit emerges from the 'C4' output of the top right cy-look-ahead ic. Thus the

final carry is available before the first level look-aheads provide their carry signals to the end Xor gates, and the Xor gates process them, so that's more than 2 gate delays earlier than the result is available.

- The V flag is generated by Xorting the final Carry with the Carry of the previous bit. The later emerges from the first level carry-lookahead circuit at the bottom right of the drawing, it is depicted as 'Cx' in the logisim model. Thus the Cx is available one gate delay earlier than the Result. Then it is compared (not shown in that drawing) with the final carry by means of a Xor gate, which executes concurrently with the end Xor gates of the adder. Therefore we have the V flag at the same time than the result.

- The problematic flag is still (and surprisingly) the Z flag, which must be computed after the Result