BigEd wrote:

Indeed, as the target speed is 1MHz, it's not fair to criticise that the design won't go at great speeds. It's not meant to, and the comment is just a temptation to scope creep.

Keep it simple, stick to your goals, and get it working. Plenty of possibilities for going further, after you have something working.

Exactly! I want to build a computer that I can understand, not brag about how fast it goes, although I may brag that I understand every last bit of how it works (once I do)...

When I got my first PC, I wondered how it "knew" where to look for DOS. Just a couple years ago, I installed Arch Linux on a computer - by hand "the Arch way", no fancy automated installers. I learned the BIOS is hard coded to look in the first 512 bytes of whatever storage is available. Now, after researching the 6502, I'm assuming modern CPUs also have reset vectors or equivalent that are hard wired and tell them where to look for the BIOS startup routine.

As I stated before, one of my goals is to mimic an old pre-Pentium era PC design (386, 486), using the ROM as a sort of BIOS, which loads programs from some sort of mass storage, most likely an SD card.

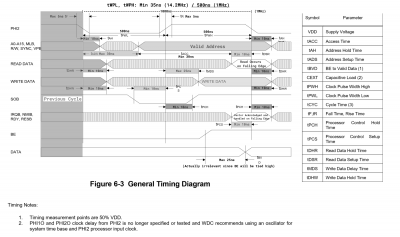

I rewatched Ben Eater's bus timing video

https://www.youtube.com/watch?v=i_wrxBdXTgM&ab_channel=BenEater again and this time I stopped it multiple times to make notes on my own timing diagram, similar to how he did it. Even he admits that the 6502's timing diagram is a bit convoluted. I grabbed a screenshot of the PDF, threw it into Paint.Net (Photoshop for poor people), added the nanosecond timings directly to the diagram, and added the definitions of the abbreviations along the side and footnotes on the bottom. Everything is on one page and I don't have to flip back and forth between two or three pages any more.

Attachment:

6502 Timing Diagram -BW.png [ 729.8 KiB | Viewed 751 times ]

6502 Timing Diagram -BW.png [ 729.8 KiB | Viewed 751 times ]

This went a long way towards fully understanding what I was looking at! It also put in plain view why chip select is tied to the high end of the clock cycle.

_________________

"To err is human, to really foul things up requires a computer!"Tried to register with my

legitimate email and never got the activation message. My spam-magnet email worked fine.

If you want to email me, please use

neamerjell@gmail.com