Unlike the NMOS parts, the 65C02 (and 65C816) will respond to RDY during write cycles. So there's really no good reason to not use wait-states to accommodate slower devices.

Speed & EEPROMs

- BigDumbDinosaur

- Posts: 9426

- Joined: 28 May 2009

- Location: Midwestern USA (JB Pritzker’s dystopia)

- Contact:

Re: Speed & EEPROMs

cbscpe wrote:

You could use a dual-rate clock.

Unlike the NMOS parts, the 65C02 (and 65C816) will respond to RDY during write cycles. So there's really no good reason to not use wait-states to accommodate slower devices.

x86? We ain't got no x86. We don't NEED no stinking x86!

Re: Speed & EEPROMs

BigDumbDinosaur wrote:

it appears that you are gating the SRAM chip select with Ø2. That is generally not good practice. [...] It's better to select the SRAM (and ROM) as soon as a valid address appears on the bus, which is early during Ø2 low

In 1988 my 65C02 got six new registers and 44 new full-speed instructions!

https://laughtonelectronics.com/Arcana/ ... mmary.html

https://laughtonelectronics.com/Arcana/ ... mmary.html

- GARTHWILSON

- Forum Moderator

- Posts: 8773

- Joined: 30 Aug 2002

- Location: Southern California

- Contact:

Re: Speed & EEPROMs

The real problem is ROM speeds though, which are at least five times as slow as SRAM speeds.

http://WilsonMinesCo.com/ lots of 6502 resources

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

Re: Speed & EEPROMs

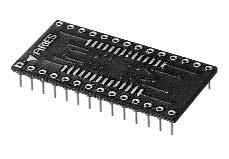

A minor side track: could you use one of these for SOJ devices? I.e. is the spacing the same with the pins as the SOJIC? Forgive my ignorance as I've never dealt with SOJ/SOJIC.

http://uk.mouser.com/ProductDetail/Arie ... mh6pEqc%3d

http://uk.mouser.com/ProductDetail/Arie ... mh6pEqc%3d

- Oneironaut

- Posts: 734

- Joined: 25 May 2015

- Location: Gillies, Ontario, Canada

- Contact:

Re: Speed & EEPROMs

The 10ns SOJ packages are easy to hand solder.

I have done this using 3 different moethods; adapter, ribbon wire to socket, and most recently, dead-bugged to socket.

Here is the part at Digikey...

http://www.digikey.com/product-search/e ... ageSize=25

Garth also has modules available.

Brad

I have done this using 3 different moethods; adapter, ribbon wire to socket, and most recently, dead-bugged to socket.

Here is the part at Digikey...

http://www.digikey.com/product-search/e ... ageSize=25

Garth also has modules available.

Brad

- GARTHWILSON

- Forum Moderator

- Posts: 8773

- Joined: 30 Aug 2002

- Location: Southern California

- Contact:

Re: Speed & EEPROMs

banedon wrote:

A minor side track: could you use one of these for SOJ devices? I.e. is the spacing the same with the pins as the SOJIC? Forgive my ignorance as I've never dealt with SOJ/SOJIC.

http://uk.mouser.com/ProductDetail/Arie ... mh6pEqc%3d

http://uk.mouser.com/ProductDetail/Arie ... mh6pEqc%3d

I have a few with different numbers of pins here. The adapter usually costs a lot more than the IC, but it sure makes things easy.

http://WilsonMinesCo.com/ lots of 6502 resources

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

Re: Speed & EEPROMs

Thanks guys.

I've already purchased 4x CY7C109D-10VXI and 3x CY7C199D-10VXI so just need to figure out if I can find adapters that are cheap enough to warrant not soldering them myself.

I've already purchased 4x CY7C109D-10VXI and 3x CY7C199D-10VXI so just need to figure out if I can find adapters that are cheap enough to warrant not soldering them myself.

- Oneironaut

- Posts: 734

- Joined: 25 May 2015

- Location: Gillies, Ontario, Canada

- Contact:

Re: Speed & EEPROMs

Oneironaut wrote:

There's also these:

http://www.ebay.co.uk/itm/New-10-PCS-SO ... 3a9479cfc5

- jac_goudsmit

- Posts: 229

- Joined: 23 Jun 2011

- Location: Rancho Cucamonga, California

- Contact:

Re: Speed & EEPROMs

Did you look at Schmartboard.com for SMD-to-DIP converter boards?

===Jac

===Jac

Re: Speed & EEPROMs

Here's another mounting method for SOJ (below).

Also I've edited my previous post to include a circuit for two wait-states. Compared with no wait states, this results in roughly quintuple (5 times) the available memory access time. /CS is presumed to go low before the start of phase two, as already discussed.

cheers,

Jeff

Also I've edited my previous post to include a circuit for two wait-states. Compared with no wait states, this results in roughly quintuple (5 times) the available memory access time. /CS is presumed to go low before the start of phase two, as already discussed.

cheers,

Jeff

Last edited by Dr Jefyll on Thu Jun 18, 2015 8:18 pm, edited 2 times in total.

In 1988 my 65C02 got six new registers and 44 new full-speed instructions!

https://laughtonelectronics.com/Arcana/ ... mmary.html

https://laughtonelectronics.com/Arcana/ ... mmary.html

Re: Speed & EEPROMs

Looking now  .

.

Brad, how do you normally keep the IC in place? A dab of hot glue? Blutack? (:D)

Brad, how do you normally keep the IC in place? A dab of hot glue? Blutack? (:D)

Re: Speed & EEPROMs

Dr Jefyll wrote:

Here's another mounting method for SOJ (below).

Also I've edited my previous post to include a circuit for two wait-states. Compared with no wait states, this results in roughly quintuple (5 times) the available memory access time. /CS is presumed to go low before the start of phase two, as already discussed.

cheers,

Jeff

Also I've edited my previous post to include a circuit for two wait-states. Compared with no wait states, this results in roughly quintuple (5 times) the available memory access time. /CS is presumed to go low before the start of phase two, as already discussed.

cheers,

Jeff

Thus I could set up the following:

$0000-$1FFF - non-swap RAM area for ZP, stack and user/program space (area always stays available)

$2000-$7FFF - swap bank area A (RAM banks A0,A1,A2,A3)

$8000-$AFFF - non-swap I/O area (area always stays available)

$B000-$FFFF - swap bank area B (banks B0, B1)

B0 will be ROM

B1 will be faster RAM

On boot, B0 is selected. It copies boot strap code to page 0

This code runs a copy of bank B0 to B1, swaps to bank B1

Code is then executed from a point in the new 'rom' area in B1

Looks do-able to me.

- Oneironaut

- Posts: 734

- Joined: 25 May 2015

- Location: Gillies, Ontario, Canada

- Contact:

Re: Speed & EEPROMs

Once you solder the 4 bent legs, the IC is pretty well affixed since it seats nice in the socket.

Here is a closeup of the operation...

viewtopic.php?f=4&t=3329

Brad

Here is a closeup of the operation...

viewtopic.php?f=4&t=3329

Brad

banedon wrote:

Looking now  .

.

Brad, how do you normally keep the IC in place? A dab of hot glue? Blutack? (:D)

Brad, how do you normally keep the IC in place? A dab of hot glue? Blutack? (:D)

- GARTHWILSON

- Forum Moderator

- Posts: 8773

- Joined: 30 Aug 2002

- Location: Southern California

- Contact:

Re: Speed & EEPROMs

Oneironaut wrote:

Once you solder the 4 bent legs, the IC is pretty well affixed since it seats nice in the socket.

Here is a closeup of the operation...

viewtopic.php?f=4&t=3329

Here is a closeup of the operation...

viewtopic.php?f=4&t=3329

http://WilsonMinesCo.com/ lots of 6502 resources

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?