Breaking 6502 apart

Re: Breaking 6502 apart

org wrote:

I updated my PLA utility...

Re: Breaking 6502 apart

6502 addict

Re: Breaking 6502 apart

Hello everyone, long time no see )

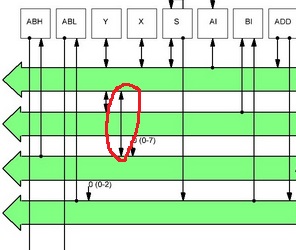

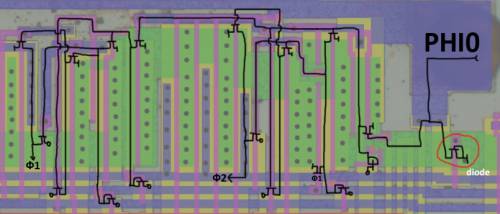

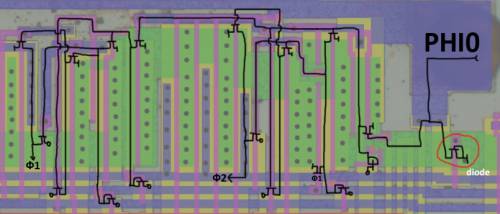

Please help me to analyse this circuit :

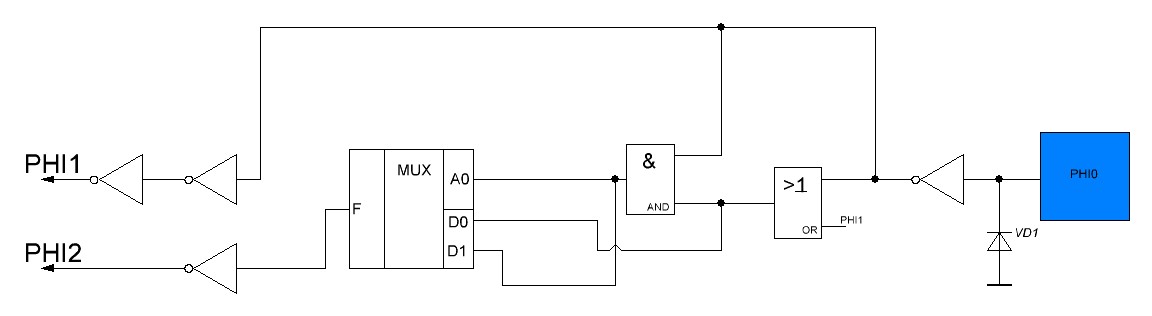

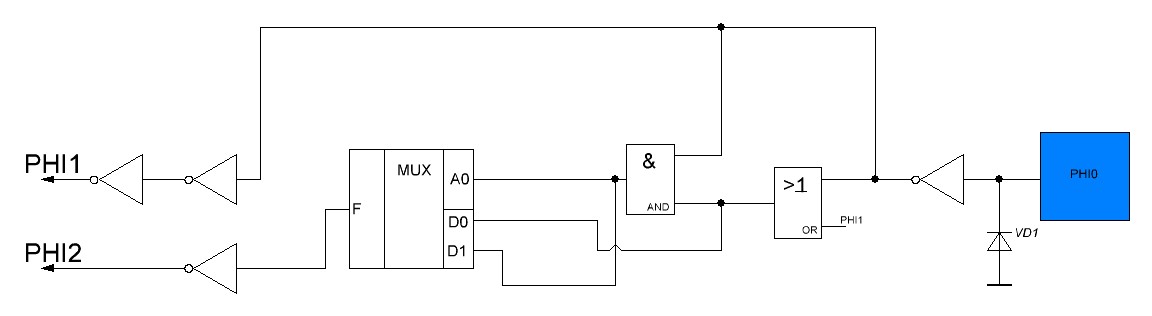

And logic representation :

The problem is following: as you know, PHI1/PHI2 is lag a little over input PHI0. But 6502 documentation says PHI1/PHI2 also have a slighty extended low period, to ensure that PHI1 and PHI2 are never high at the same time.

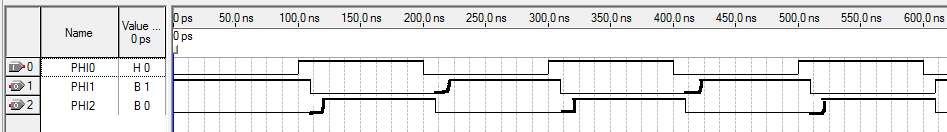

Can someone simulate this circuit and check for PHI1/PHI2 timing diagram ?

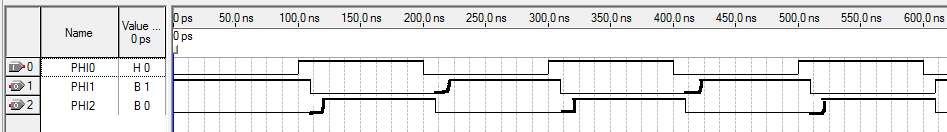

It should be someting like that :

Please help me to analyse this circuit :

And logic representation :

The problem is following: as you know, PHI1/PHI2 is lag a little over input PHI0. But 6502 documentation says PHI1/PHI2 also have a slighty extended low period, to ensure that PHI1 and PHI2 are never high at the same time.

Can someone simulate this circuit and check for PHI1/PHI2 timing diagram ?

It should be someting like that :

6502 addict

Re: Breaking 6502 apart

Hi Org

please check against this circuit, which looks more plausible: viewtopic.php?f=1&t=2412#p24074

I followed the instructions at viewtopic.php?p=13550#p13550 and was able to capture these images of a simulation of the 6502 netlist (as found in Peter Monta's github project): The nodenames & numbers are from the visual6502 netlist.

Cheers

Ed

please check against this circuit, which looks more plausible: viewtopic.php?f=1&t=2412#p24074

I followed the instructions at viewtopic.php?p=13550#p13550 and was able to capture these images of a simulation of the 6502 netlist (as found in Peter Monta's github project): The nodenames & numbers are from the visual6502 netlist.

Cheers

Ed

Re: Breaking 6502 apart

My friend, more enlightened in the hardware stuff said it is "asymmetric cascade inverter", which delays the rising edge, so it seems that the lower level of PHI1/PHI2 is longer than the upper.

This mean Balazs clock envelopes are slighty incorrect.

This mean Balazs clock envelopes are slighty incorrect.

6502 addict

Re: Breaking 6502 apart

Removed all circuits from circuitlab. Dont like it greedy politics.

Now converting all circuits into sPlan format and doing double check.

Latest circuitlab circuits can be found here (may be outdated in near future) : http://breaknes.com/files/6502/6502_circuitlab.zip (2 MB)

Also I want to introduce project wiki : http://wiki.breaknes.com (currently only on russian)

Now converting all circuits into sPlan format and doing double check.

Latest circuitlab circuits can be found here (may be outdated in near future) : http://breaknes.com/files/6502/6502_circuitlab.zip (2 MB)

Also I want to introduce project wiki : http://wiki.breaknes.com (currently only on russian)

6502 addict

Re: Breaking 6502 apart

Revised approach to the device debugger. Now its made in the form of a scalable circuit image layout with controls located on top of it and also scaled along with a picture.

Simulated module passing list of "triggers" to the core, which can be controlled through debug interface.

Going to make it as tabbed interface for different parts, when I get rid with Qt

Execution simply made by pressing "Next Step" button, which execute "Step" procedure of simulated ciruit and toggles input clock.

Simulated module passing list of "triggers" to the core, which can be controlled through debug interface.

Going to make it as tabbed interface for different parts, when I get rid with Qt

Execution simply made by pressing "Next Step" button, which execute "Step" procedure of simulated ciruit and toggles input clock.

6502 addict

Re: Breaking 6502 apart

Hanson's diagram shows SB also connecting to ADH through pass gates...

Re: Breaking 6502 apart

Oh! I didn't see it...

Re: Breaking 6502 apart

Complete 6502 interrupt processing circuit.

And short description.

Input pads /NMI, /IRQ, /RES are saved in input triggers.

Interrupt generation circuit additionally requires 6 and 7 cycles (since they do not arrive from decoder) (control signals BRK6E and BRK7). Control signal BRK6E begins during the PHI2 of 6th cycle and ends during PHI1 of 7th cycle (overlap 6 and 7 cycle). This is done in order to determine the edge of the signal /NMI. Edge detection of /NMI based on classic edge detect circuit (two cross-coupled RS-triggers).

The signal /RES is further saved on the RESET FLIP/FLOP, as it is required for other random logic circuits (in particular for a special control of R/W pad during reset).

The fact of the arrival of any interrupt reflected on B-flag, the output of which (B_OUT) forces the processor to execute BRK instruction (opcode 0x00). Thus developers unified processing of all interrupts.

Last small circuit generates an interrupt address (or vector) (control lines 0/ADL0, 0/ADL1 and 0/ADL2), which is reflected on 3 bits of the address bus.

The interesting thing is affection of BR2 (Branch T2) and T0 (Execute Cycle 0) control lines on interrupt detection (IRQ CHECK).

In case you wish to play with it in Logisim, you can grab it from SVN:

https://code.google.com/p/breaks/source ... 2/INT.circ

PS. All D-latches are level-triggered. Those one with invertor are PHI1 driven (and in turn PHI2 driven without it).

And short description.

Input pads /NMI, /IRQ, /RES are saved in input triggers.

Interrupt generation circuit additionally requires 6 and 7 cycles (since they do not arrive from decoder) (control signals BRK6E and BRK7). Control signal BRK6E begins during the PHI2 of 6th cycle and ends during PHI1 of 7th cycle (overlap 6 and 7 cycle). This is done in order to determine the edge of the signal /NMI. Edge detection of /NMI based on classic edge detect circuit (two cross-coupled RS-triggers).

The signal /RES is further saved on the RESET FLIP/FLOP, as it is required for other random logic circuits (in particular for a special control of R/W pad during reset).

The fact of the arrival of any interrupt reflected on B-flag, the output of which (B_OUT) forces the processor to execute BRK instruction (opcode 0x00). Thus developers unified processing of all interrupts.

Last small circuit generates an interrupt address (or vector) (control lines 0/ADL0, 0/ADL1 and 0/ADL2), which is reflected on 3 bits of the address bus.

The interesting thing is affection of BR2 (Branch T2) and T0 (Execute Cycle 0) control lines on interrupt detection (IRQ CHECK).

In case you wish to play with it in Logisim, you can grab it from SVN:

https://code.google.com/p/breaks/source ... 2/INT.circ

PS. All D-latches are level-triggered. Those one with invertor are PHI1 driven (and in turn PHI2 driven without it).

6502 addict

Re: Breaking 6502 apart

Random logic + Dispatcher.

Everything seems to work fine

Next step : connect all things together, try to execute some instruction and examine controls to bottom part.

Everything seems to work fine

Next step : connect all things together, try to execute some instruction and examine controls to bottom part.

6502 addict

Re: Breaking 6502 apart

Here we go !

Complete top part 6502 simulation in discrete logic elements!

https://code.google.com/p/breaks/source ... ANDOM.circ

Enjoy

Sadly its impossible to simulate full 6502 in Logisim, since it doesn't support bidirectional wires and I have no clue how to implement bus-to-bus connections there.

I'm going to implement it in Verilog, check on CPLD and rewrite on C, for my emulator project.

PS. I fixed some bugs in random logic, check updated version in attach.

Complete top part 6502 simulation in discrete logic elements!

https://code.google.com/p/breaks/source ... ANDOM.circ

Enjoy

Sadly its impossible to simulate full 6502 in Logisim, since it doesn't support bidirectional wires and I have no clue how to implement bus-to-bus connections there.

I'm going to implement it in Verilog, check on CPLD and rewrite on C, for my emulator project.

PS. I fixed some bugs in random logic, check updated version in attach.

6502 addict