Code: Select all

tcstate[1] <= tcstate[0];

if(rdy0)

tcstate[5:3] <= 3'b111;

else

tcstate[5:3] <= tcstate[4:2];

tcstate[2] <= !sync;As far as I can tell, T0 is driven high after PLA34 is high (which goes high when T0 goes low). i.e.

Code: Select all

assign pla[34] = !tcstate[0];

if(pla[34]) tcstate[0] <= 1'b1;Code: Select all

if(rdy0 & tcstate[0]) tcstate[0] <= 1'b0;Context:

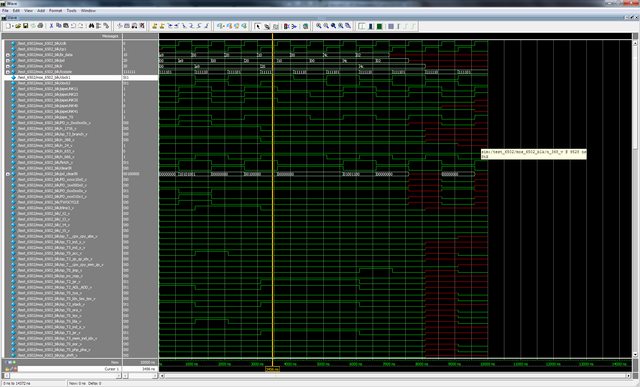

I am working to implement a 6502 core in Verilog that is gate-level accurate with the work published by visual6502.org. I'm doing it for my own educational purposes, so I don't mind if others have done this already.

I don't know much about reading physical chip layouts; how to read the transistors and wires and then piece those together into gates. Which is exactly why I'm doing this!

T0 seems to control when the next instruction is fetched, so it's important to have before I can get even the most basic parts of my 6502 core working

P.S. Sorry if this is posted to the wrong section. I'm working in Verilog, so I would have posted it in that section, but my question isn't actually related to verilog.

Any help is greatly appreciated. Thank you.