Hi y'all, long time reader and first time poster.

I've been enjoying my breadboard build, and an Apple 1 SBC from eBay, but I want to put copper (and my money) where my mouth is and build out some PCBs. I also own a lot of gear from the RC2014 and "Small Computer Central" ecosystems, and because of that, I've decided to design a z50 Bus card. If you don't know it, z50 is a hobbyist bus designed by Ole Lians and is well documented. Specification is here:

http://linc.no/products/z50bus/.

They describe how to adapt a 6502 to the bus, so I took that as a starting place, along with the 6502 primer and lots of posts here on the forum.

Attachment:

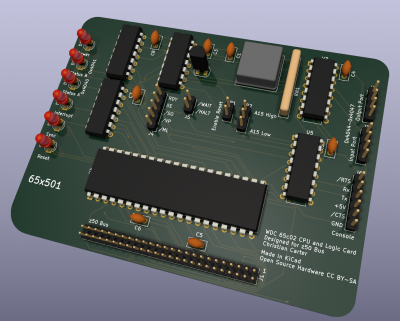

File comment: 3d render

Screen Shot 2023-03-04 at 11.08.20 PM.png [ 1.56 MiB | Viewed 39232 times ]

Screen Shot 2023-03-04 at 11.08.20 PM.png [ 1.56 MiB | Viewed 39232 times ]

My board is designed to provide the CPU and bus logic signals, and to be compatible with the following cards:

As well as being generally compatible with other z50 bus cards that don't rely on the z80's special interrupt handling (e.g. not the z80 CTC/PIO/SIO accessories).

The board generates the following z50 bus signals.

- /RD and /WR (thanks to BDD's great circuit)

- /IOReq at $4000-$8000 (thanks to Garth's memory map

- /MReq (simple NOT /IOReq)

- /M1 (simple NOT SYNC)

In order to support the standard z50/z80 memory map and existing memory cards, there is a jumper to export either A15 or /A15 to the bus on the A15 line. By selecting the /A15 option, the existing memory card can be used, its RAM and Flash accesses will be flipped.

There's eight 1-bit inputs and eight 1-bit outputs onboard, selected by the /PORT signal. A 74HC4075 generates /PORT as well as the chip enables (/PORT & /IOReq & the appropriate read or write). These offer a bit-banged UART, two status LEDs that can be controlled by the user program, and four bits on headers for user experiments. The output circuit comes from SCC's SC519/SC516 designs, and I just tried to flip/reverse it for the input port.

BE/RDY/SO/VP/ML are all just tied high (or left floating where appropriate) but a header exposes them, in case I want to bodge on some logic later. The bus standard specifies /WAIT and /HALT signals but no existing peripherals use them, and I haven't quite figured out what splitting RDY for that would look like anyway.

I'm attaching a draft schematic (in color and B&W). I'd appreciate any comments, suggestions, or pointing out any mistakes I've made. All logic is 74HCxx series (even if I maybe forgot to update the symbol) running at 5V.

A few specific points I'd like feedback on:

1) the single bit ports all use the LSB of the data bus for actually communicating with the processor. Is there a bit that's easier to read/write consistently, that I should consider instead of D0?

2) Does this Mux actually work the way I'm trying to use it?

3) I stuck all the resistors for the LEDs under the CPU, I'm thinking a second resistor net is a better idea, but I haven't priced components yet. practically, how does the price of a thru-hole resistor net compare to that of a handful of thru-hole resistors?

4) I wanted to provide an LED for /HALT but I ran out of gates to even invert it, let alone figure out how to connect it to RDY. Is there any simplification in my logic that would bring net me a spare inverter?

Many thanks!