Page 2 of 2

Re: 'Qualifying' write operations

Posted: Wed Jul 14, 2021 9:56 pm

by J64C

Yeah, but the point of it is to illustrate that the write pulse is guaranteed to be set before the address setup (as per the data sheets).

If in practice, it happens the other way around, then great, we got lucky! I prefer to alway work for worse case every time.

Re: 'Qualifying' write operations

Posted: Thu Jul 15, 2021 1:26 pm

by BigEd

I think you might miss part of hoglet's point there...

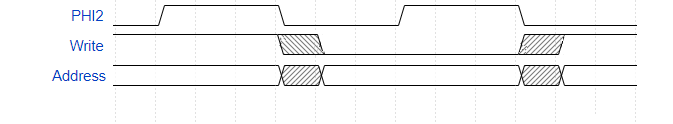

The trailing edge of Write, which is caused by Phi2's falling edge, and lags it by an indeterminate amount, is a grey area. As it coincides with the grey area of the address bus, there's a double unknown: you don't know if you're writing, and you don't know where to.

On paper and whiteboards, I like sometimes to put a wibbly arrow from the edge which causes something to the event which it causes. It's more difficult to do this in a graphic. But I find it really helps to show why things happen in the order that they do happen. Failing the wibbly arrow, it can help to shift things slightly: things caused by something can be shown as happening very slightly later.

So, that's a couple of suggestions for an improvement to a diagram which is already a useful diagram: thanks for drawing and sharing!

Re: 'Qualifying' write operations

Posted: Thu Jul 15, 2021 2:27 pm

by Dr Jefyll

it coincides with the grey area of the address bus

Indeed -- like this:

- qualified_write.png (5.12 KiB) Viewed 1677 times

-- Jeff

Re: 'Qualifying' write operations

Posted: Thu Jul 15, 2021 5:04 pm

by BillO

it coincides with the grey area of the address bus

Indeed -- like this:

qualified_write.png

-- Jeff

Jeff, what do you use to create your timing diagrams?

Re: 'Qualifying' write operations

Posted: Thu Jul 15, 2021 5:48 pm

by hoglet

It looks like WaveDrom, which is an online editor:

https://wavedrom.com/editor.html

Re: 'Qualifying' write operations

Posted: Thu Jul 15, 2021 7:09 pm

by Dr Jefyll

Jeff, what do you use to create your timing diagrams?

I don't know how J64C

created the diagram. Could've been WaveDrom, as hoglet suggested. I merely edited the bitmap that was already there, using Paint Shop Pro (which is equivalent to PhotoShop).

So, I'm working at the pixel level. PSP doesn't "understand" timing diagrams. But the program is excellent, and I've had enough practice that I've gotten pretty speedy.

And I can edit almost anything. Nearly every image I post on this forum comes from PSP, including

alterations to the work of others, and original images of my own (including my animated avatar).

-- Jeff

Re: 'Qualifying' write operations

Posted: Tue Dec 21, 2021 7:24 am

by J64C

From what I understand the VIA IC's don't require write qualification as they 'know' about how the W65C02's work. Is this correct?

What happens if you do still use the qualified write circuit on a VIA? Will it still function correctly?

Re: 'Qualifying' write operations

Posted: Tue Dec 21, 2021 7:40 am

by GARTHWILSON

From what I understand the VIA IC's don't require write qualification as they 'know' about how the W65C02's work. Is this correct?

What happens if you do still use the qualified write circuit on a VIA? Will it still function correctly?

Re: 'Qualifying' write operations

Posted: Tue Dec 21, 2021 10:23 am

by J64C

Interesting! Thank you so much for the advice!

Re: 'Qualifying' write operations

Posted: Tue Dec 21, 2021 4:33 pm

by barrym95838

I can't be sure (because I did it over 30 years ago) but I think I got away with un-qualified writes on a

small breadboard project with a 'c802, PIA, EPROM and SRAM. ISTR running it at 1 MHz and 2 MHz without incident. Maybe it was dumb luck?

Re: 'Qualifying' write operations

Posted: Tue Dec 21, 2021 7:59 pm

by GARTHWILSON

I ran into this again when I made an I/O board for our son's Commodore 64 to control his model railroad setup when he was in junior high decades ago. Since the C64's select outputs to the port didn't go true until phase 2 did, I had to artificially delay the rise of phase 2 but not the fall. (I don't remember the C64 details anymore, and I gave away all our C64 computers, peripherals, accessories, books, etc. several years ago.) You can see my circuit at http://6502.org/users/garth/projects.php?project=7 . (The timings there were for the C64 which runs at only 1MHz, and the VIAs I used were probably rated for 1MHz too, definitely not more than 2MHz.)

Re: 'Qualifying' write operations

Posted: Tue Dec 21, 2021 9:32 pm

by Dr Jefyll

I think I got away with un-qualified writes

The thing about un-qualified writes is, you might not be aware you have a problem. By intentionally writing to address 1234, for example, you might also unintentionally alter memory at some other address(es).

If the address(es) affected happen to be unused then the problem may go unnoticed.

-- Jeff

Re: 'Qualifying' write operations

Posted: Wed Dec 22, 2021 12:17 am

by BillO

I think I got away with un-qualified writes

The thing about un-qualified writes is, you might not be aware you have a problem. By intentionally writing to address 1234, for example, you might also unintentionally alter memory at some other address(es).

If the address(es) affected happen to be unused then the problem may go unnoticed.

-- Jeff

I learned this the hard way a few years back (with the help of the great people here). In my early years I seemed to get away with all sorts of nonsense. However, when I tried that with updated chips and memory .. well they just did not seem to have the sense of humor the stuff available back in circa 1979 did. Now I qualify both read and write. Makes for less head banging.

The 65XX chips do their own read and/or write qualifying. They expect an unaltered R/W along with phi2 to manage the timing. Supplying a pre-qualified R/W signal might not leave them enough time to figure things out. That old accumulated propagation delay thing..

Re: 'Qualifying' write operations

Posted: Wed Dec 22, 2021 8:59 am

by J64C

I ran into this again when I made an I/O board for our son's Commodore 64 to control his model railroad setup when he was in junior high decades ago. Since the C64's select outputs to the port didn't go true until phase 2 did, I had to artificially delay the rise of phase 2 but not the fall. (I don't remember the C64 details anymore, and I gave away all our C64 computers, peripherals, accessories, books, etc. several years ago.) You can see my circuit at http://6502.org/users/garth/projects.php?project=7 . (The timings there were for the C64 which runs at only 1MHz, and the VIAs I used were probably rated for 1MHz too, definitely not more than 2MHz.)

The C64 is a tricky beast. The CPU only gets the bus on the high clock and the VIC2 chip gets it on the lock phase (forcing the CPU to high Z itself). Maybe it was something along those lines that influenced your design at the time.

Re: 'Qualifying' write operations

Posted: Sat Dec 25, 2021 5:10 pm

by barrym95838

In my early years I seemed to get away with all sorts of nonsense.

Oh my goodness, yes. I made it through my early "invincible" twenties with the loss of only a few hundred thousand brain cells, but luck was definitely on my side, because things could have been much, much worse.