In support of my arguments over on this thread:

http://forum.6502.org/viewtopic.php?f=4&t=6594I'm going to do a few real-life experiments. This first one is to see the drive capability of a 74LSxx chip in various environments. I'll check it out in a typical situation where it's original designers expected it to live .. driving 6 full TTL loads. The test load is a 7404. Next I'll check out how well we can drive a load more in tune with our projects .. 6 CMOS loads (a 74HC04). The finally I will overload it beyond the worst case specifications (6 full TTL loads + 8.2K resistor) and see how it does.

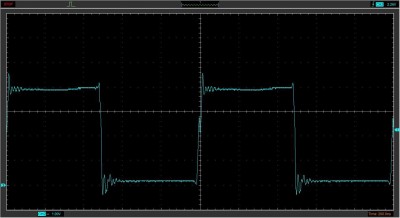

Here is it driving the 6 full TTL loads. Measured current draw at the high level is 114uA.

Attachment:

6ttl.jpg [ 78.7 KiB | Viewed 1617 times ]

6ttl.jpg [ 78.7 KiB | Viewed 1617 times ]

We can see, as expected it fully meets and nicely exceeds specifications for both TTL and CMOS environments.

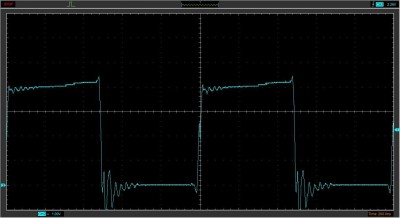

Now let's have a look at it driving the 6 CMOS loads. Measured current at the high level is 0.58uA. This is basically an open circuit form the perspective of the 74LS chip.

Attachment:

6cmos.jpg [ 80.05 KiB | Viewed 1617 times ]

6cmos.jpg [ 80.05 KiB | Viewed 1617 times ]

The lack of any reasonable load has this ringing a little, but the 74LS output has absolutely no problem exceeding CMOS input specifications. This is basically no-load performance of the chip. I suspect it would have no issue driving 50 worse case CMOS loads, excepting faulty chips.

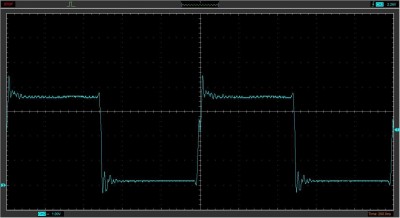

Now let's over-load the thing. 6 full TTL loads plus a 8K2 resistor. Measured current is 532uA. This would amount to 13 worst case full TTL loads or about 5,000 typical CMOS loads (ignoring capacitance). Most of us would not exceed that (I think).

Attachment:

6ttl8k2.jpg [ 79.38 KiB | Viewed 1617 times ]

6ttl8k2.jpg [ 79.38 KiB | Viewed 1617 times ]

Even under these conditions it betters typical CMOS requirements and beats the usual worst case (.7Vcc). It certainly far exceeds "worst case" TTL requirements.

Next I'll test some typical RAM, ROM and PLD devices to see if we should wonder too much why they actually work when the out dated spec sheet test conditions say they might, rarely if ever, not work.