What about the hardware part of this?

Usually the hardware varies from pretty darn simple to mildly challenging. But you mentioned an

un-usual goal, and I'll briefly deal with that before addressing commonplace scenarios.

A 16-bit data bus is an unusual goal, and in

this post I show how a couple of latches and tristate buffers can implement that, for purposes such as connecting to that S1D13506 chip of yours. And your thread

here deals with much the same subject. Sadly, 16-bit transfers don't double the speed of everything. That's because the '816 itself can only move one byte at a time over its 8-bit bus. But there is a significant speedup from having less code to execute. Specifically, there are fewer

instruction bytes to fetch when only a single, 16-bit transfer is coded, as compared to coding two 8-bit transfers.

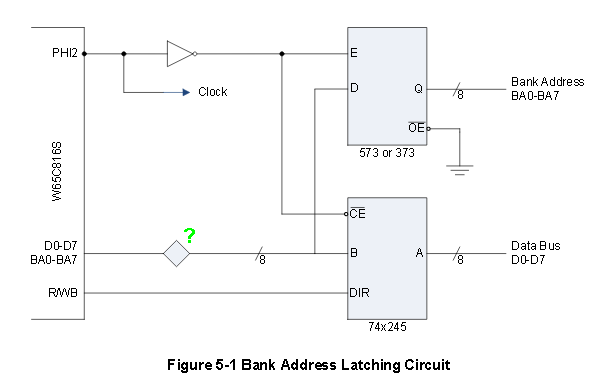

Moving to a more commonplace setting, most of us have seen the simple recipe below, taken from the '816 datasheet. (BTW I think the weird little diamond symbol merely denotes that that part of the bus is bi-directional.

)

- 5-1.png (7.73 KiB) Viewed 3780 times

This is not a complicated circuit, nor does it involve a lot of chips. And it'll "play nice" with the rest of the system. Data Bus D0-D7 is very happy go lucky (ie, undriven 50% of the time, and thus extremely tolerant in regard to contention issues), and the '573 makes all the Bank Address bits available just as if the '816 had had 8 extra pins added. IMO this simple circuit results in a setup that's just as friendly as a 6502 or 'C02. Highly recommended. Just follow the recipe!

It's possible to deviate from the recipe and get an even simpler setup. The '573 can be omitted if you only want 64K and thus have no use for the Bank Address bits. And some forumites report success with bypassing (ie, omitting) the '245... which means memory and peripherals will "see" the BA bits on their data pins during Phi2-low (instead of the bus floating at this time). I'm not surprised by those folks' success but IMO bypassing the '245 may lead to trouble for beginners, whom I encourage to stick with the recipe.

-- Jeff