Thanks, Ed.

What now follows is the "Klendathu edition": plenty of bugs at a considerable size,

because it had been a work in progress... and it wasn't properly "unmounted".

Means the register settings for generating a picture might be a little bit different from the 6545.

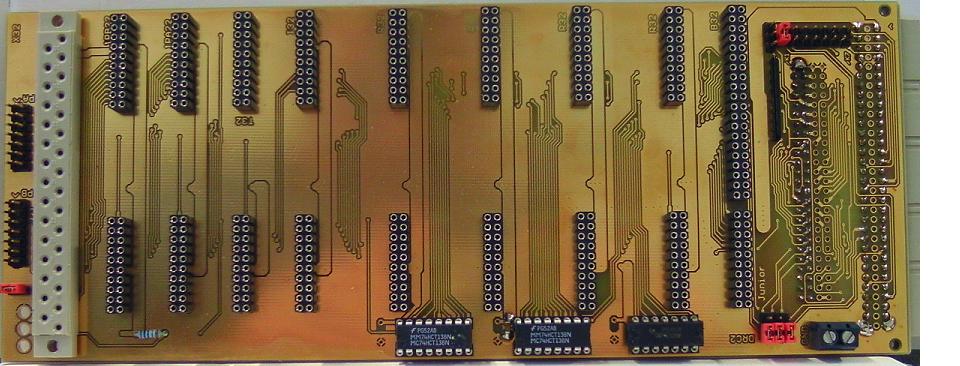

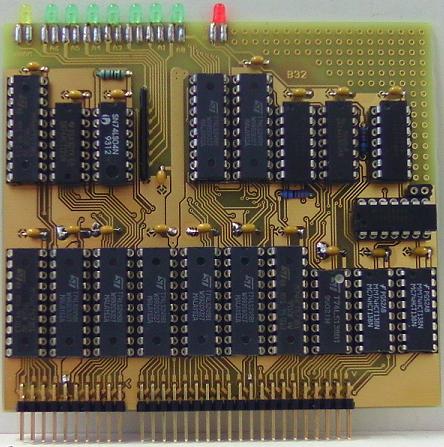

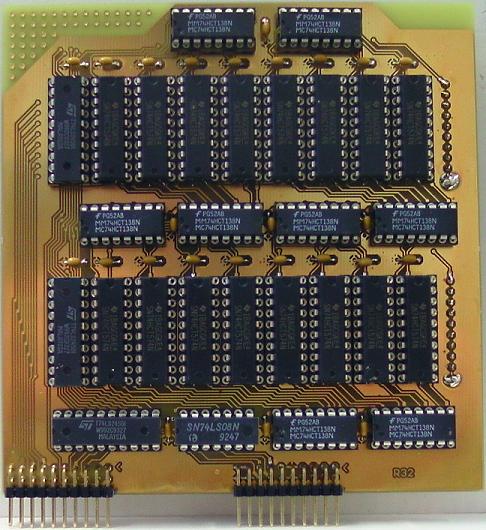

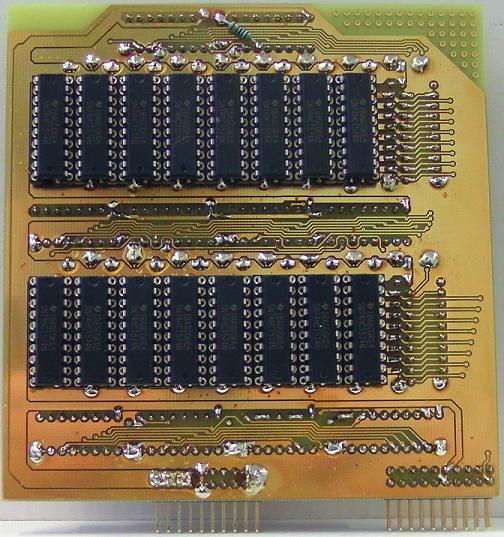

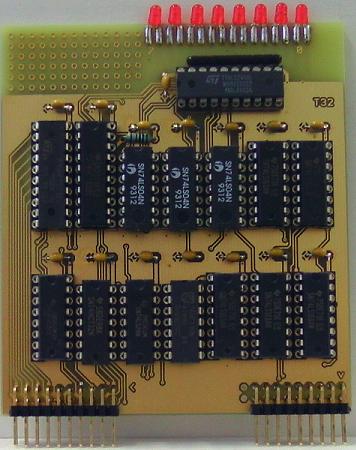

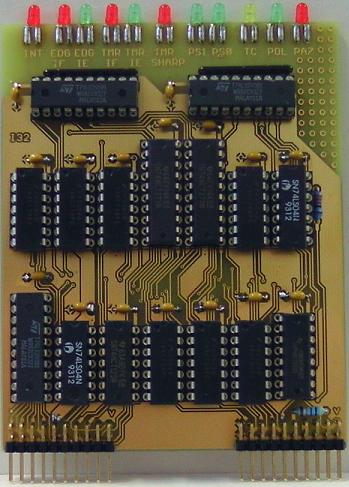

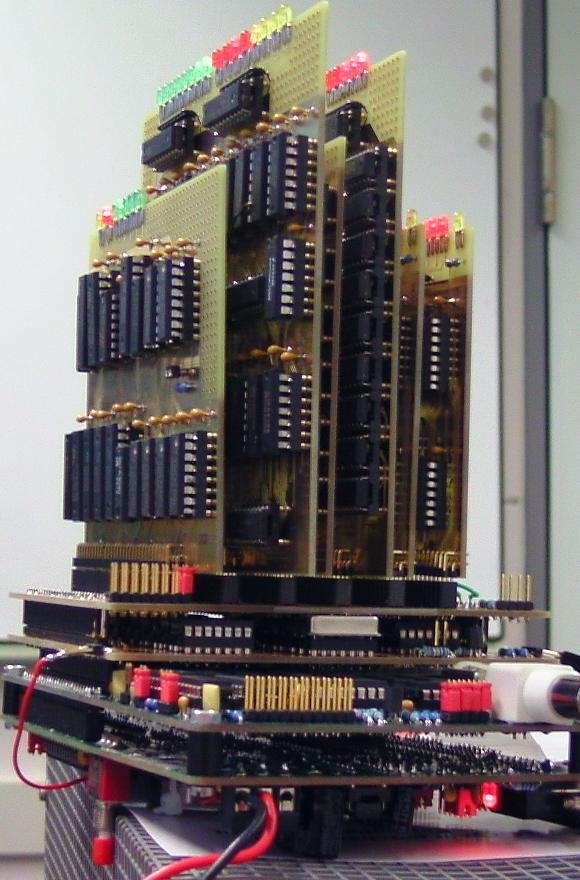

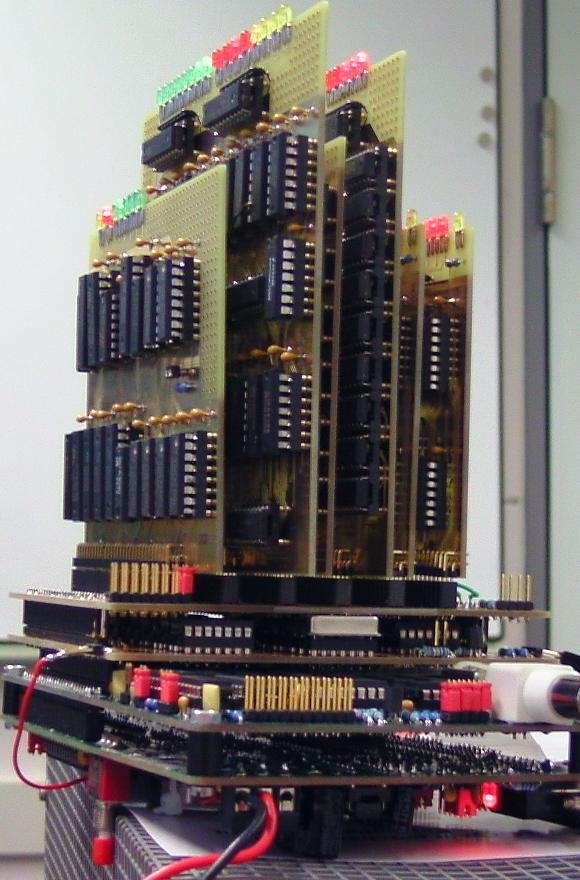

X45, experimental 6545 TTL implementation.

16 Bit video address output (instead of 14 Bit), transparent latches in the address output lines

for compensation of bus hold timing issues, and IIRC it was a three-state output.

Interlaced mode with some conceptual bugs, also sort of a horizontal scrolling mode where

one line of characters is 256 Bytes.

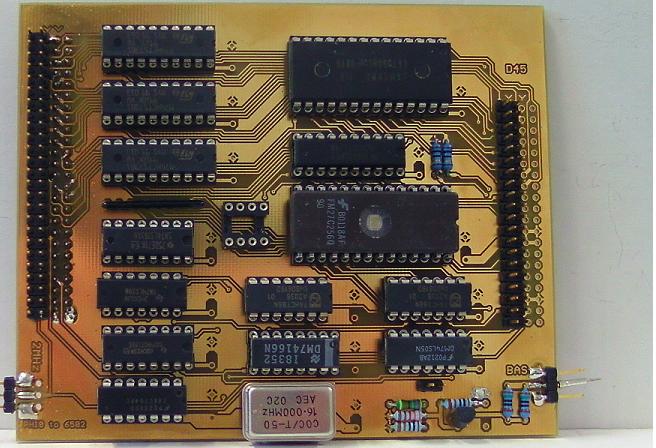

D45 demonstrator PCB (for generating a video signal) was plugged between the computer and the

X45 backplane.

Plugged into the X45 backplane, we have:

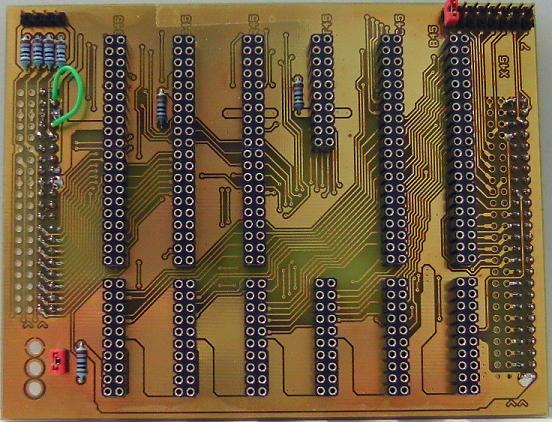

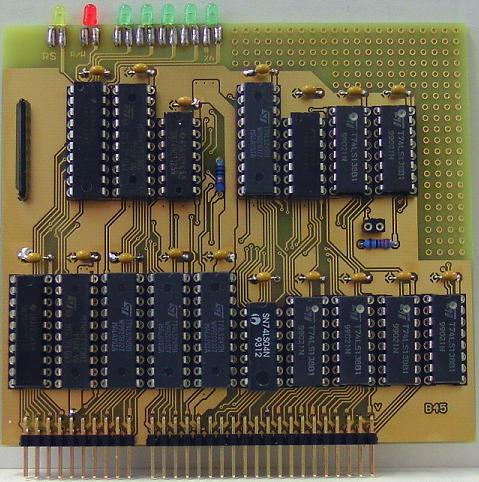

1* B45, bus interface

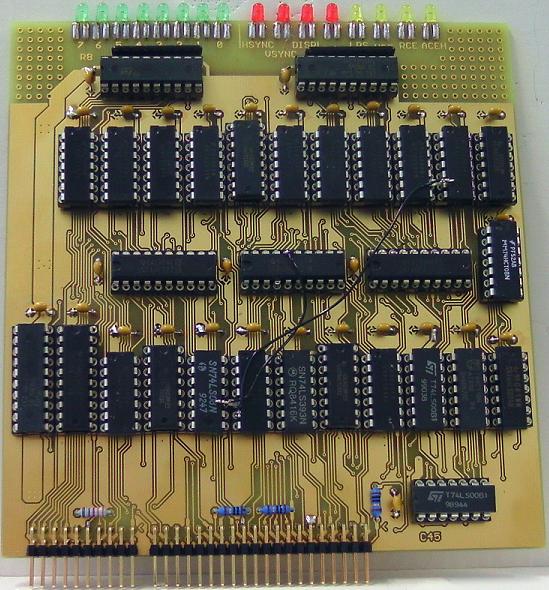

1* C45, the control module

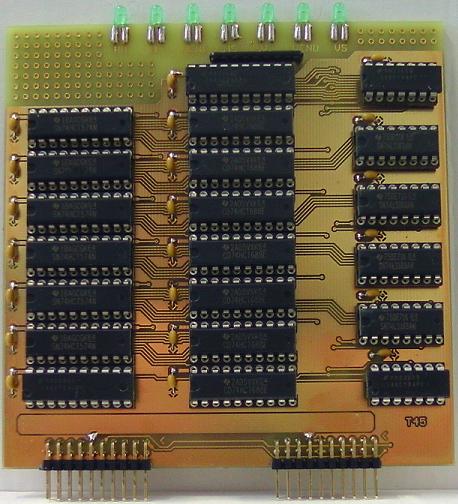

1* T45, horizontal\vertical timing module

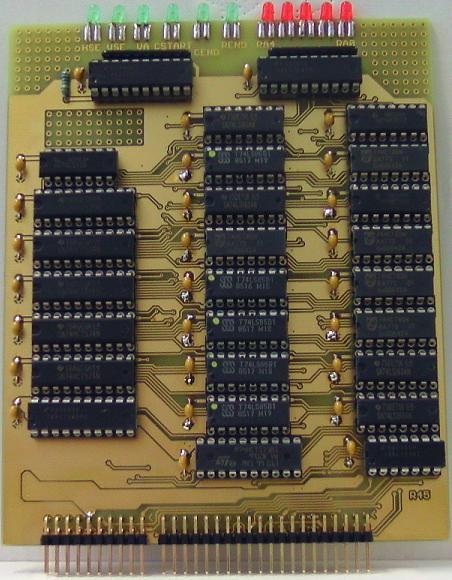

1* R45, raster timing module

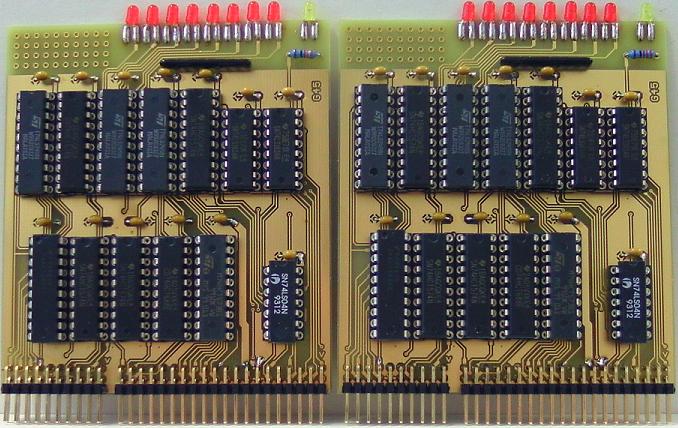

2* G45, two video address generator modules