I can give a schematic if you like but the setup is pretty simple.

Code: Select all

Apple IIe VIA

A3:0 -> RS3:0

D7:0 -> D7:0

/RES -> /RES

R/W -> R/W

/IOSEL -> CS2

/A7 -> CS1

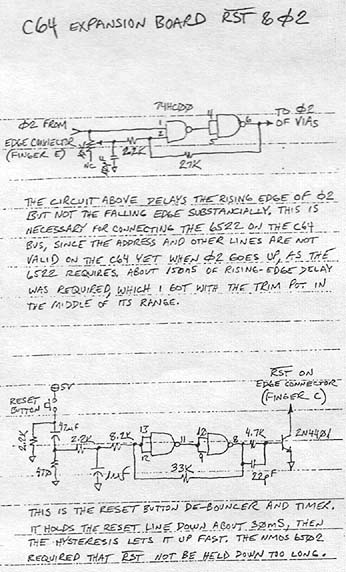

For the clock, I use PHI0 inverted 3 times to add a slight delay. I got that circuit idea from the Mockingboard clone by Bill Garber.

I have my prototype in slot 4. So this means with /IOSEL and an inverted A7, I get the following addresses:

Code: Select all

$C400 - ORB

$C401 - ORA

$C402 - DDRB

$C403 - DDRA

But I have one issue. In order for me to set a value to ORA like 128, I must set DDRA every time! So if I change ORA to 129, all my LED's go blank. I set DDRA again and 129 lights up.

What am I doing wrong? Surely this can't be right.

Here is the actual BASIC code I'm using:

Code: Select all

10 POKE 50179, 255

20 FOR A = 0 TO 255

30 PRINT A

40 POKE 50177, A

45 POKE 50179, 255

50 NEXT A

That works. But if I remove line 45, all of the LED's are blank.

Thanks