Breaking 6502 apart

Re: Breaking 6502 apart

I think you can treat it all as digital, in the sense that a transistor is a switch. But it is bidirectional... And you can't divide up the circuit purely into neat logic gates. There are some interesting combinations.

By the way, the dynamic latches are the exact reason why a single stepping circuit must be careful about whether it stops with the clock high or low. One case will be fine, the other will have the leaking storage and will not be reliable.

Cheers

Ed

By the way, the dynamic latches are the exact reason why a single stepping circuit must be careful about whether it stops with the clock high or low. One case will be fine, the other will have the leaking storage and will not be reliable.

Cheers

Ed

Re: Breaking 6502 apart

Thanks Ed, things become more clear to me.. )

50 kHz makes those 2 ms discharge rate )

At 500 kHz halfclock will last only 2us, its 1000 times shorter than discharge period )

So in order to recognize such capacitors I just need to pay attention on long polysilicon wires ?

50 kHz makes those 2 ms discharge rate )

At 500 kHz halfclock will last only 2us, its 1000 times shorter than discharge period )

So in order to recognize such capacitors I just need to pay attention on long polysilicon wires ?

6502 addict

Re: Breaking 6502 apart

Oh, I know.... When I see mosfets connected in parralel next time, I will add capacitor in schematics =)

Edit: like that :

Edit: like that :

6502.org wrote:

Image no longer available: http://ogamespec.com/imgstore/whc4fed54d25dd47.jpg

6502 addict

Re: Breaking 6502 apart

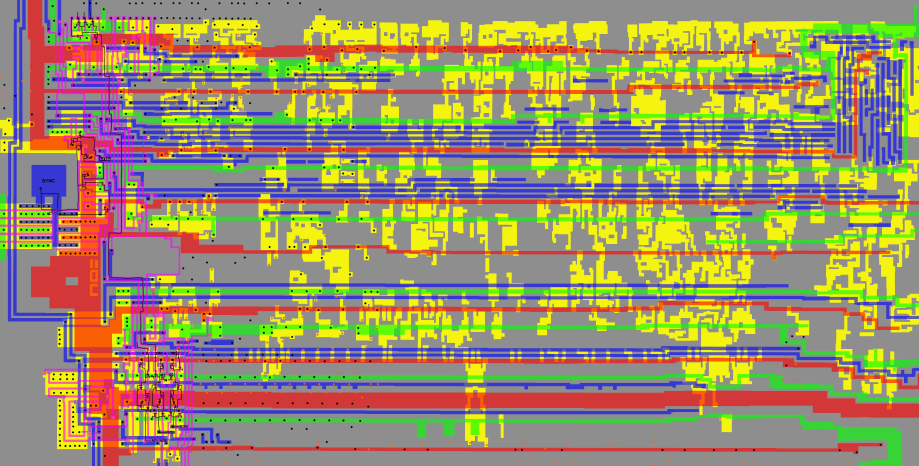

Well, you won't always have two transistors - in fact, usually you'll only have one. You'll see these nodes in the timing shift register in the first picture you posted - at top right there's a master-slave flip-flop made of two dynamic latches. More or less.

But you probably only want to annotate a capacitor when the latch is single and there's no recirculation.

But you probably only want to annotate a capacitor when the latch is single and there's no recirculation.

Re: Breaking 6502 apart

Wrote small script which helps to understand which instructions are affected by decoder.

http://ogamespec.com/6502/decoder.htm

Type IR-line into input fiels and press "Decode". Script will highlight affected opcodes.

Example : XXX110X1

http://ogamespec.com/6502/decoder.htm

Type IR-line into input fiels and press "Decode". Script will highlight affected opcodes.

Example : XXX110X1

6502.org wrote:

Image no longer available: http://ogamespec.com/imgstore/resized_w ... a80ba4.jpg

6502 addict

Re: Breaking 6502 apart

Neat! It wasn't working for me at first, but I realised I was hitting 'Enter' rather than clicking on the button.

Re: Breaking 6502 apart

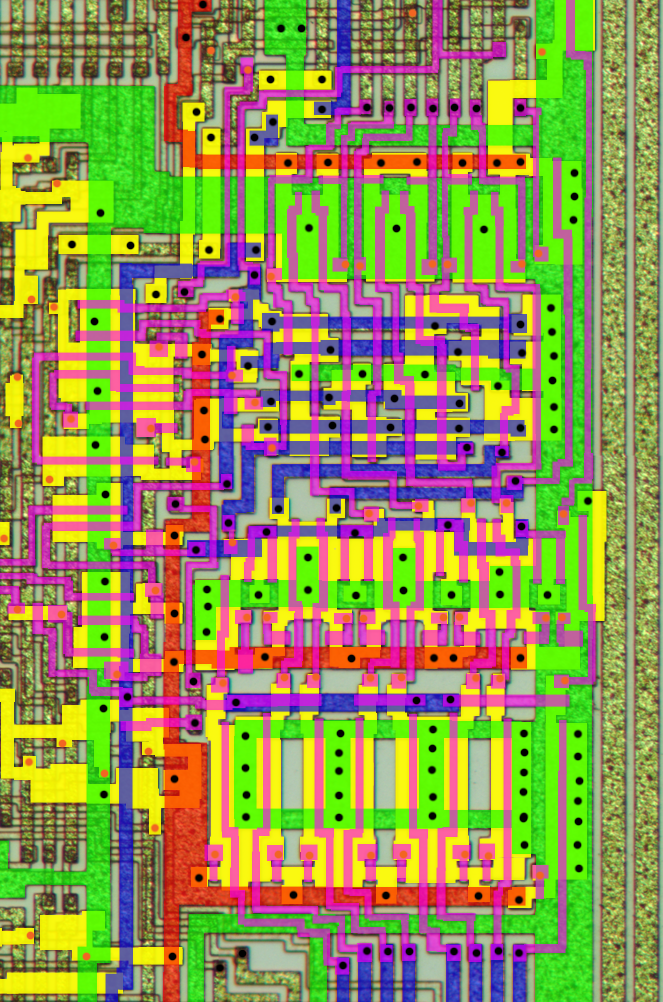

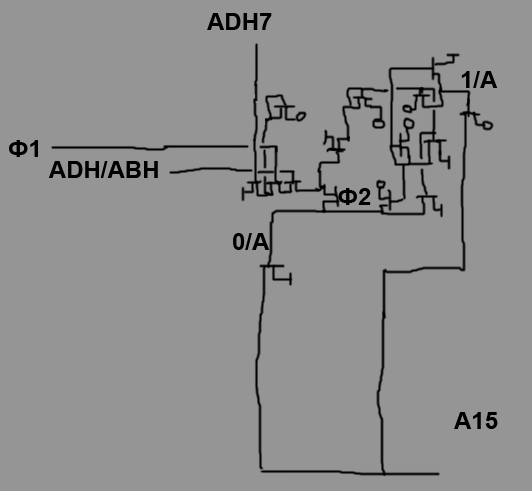

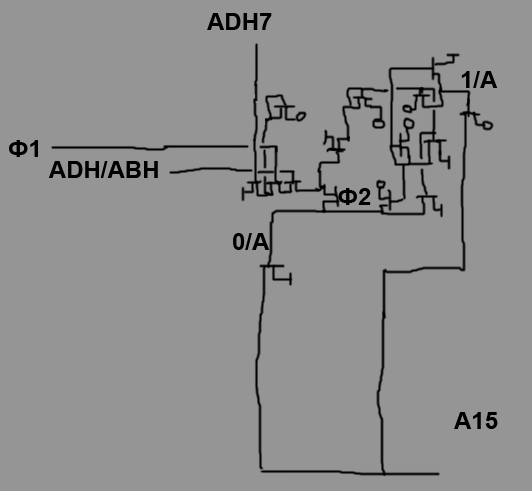

Todays speccy : Address pin

Bonus: Youtube videos, capturing my 6502 tracing skills

Part 1 : preparations

http://www.youtube.com/watch?v=dj-DcMYihp4

Part 2 : color scheme

http://www.youtube.com/watch?v=wTJygx3VAXY

http://www.youtube.com/watch?v=_Z0O-IdJRQc

Part 3 : transistor level

http://www.youtube.com/watch?v=y-q5643WVno

Bonus: Youtube videos, capturing my 6502 tracing skills

Part 1 : preparations

http://www.youtube.com/watch?v=dj-DcMYihp4

Part 2 : color scheme

http://www.youtube.com/watch?v=wTJygx3VAXY

http://www.youtube.com/watch?v=_Z0O-IdJRQc

Part 3 : transistor level

http://www.youtube.com/watch?v=y-q5643WVno

6502 addict

Re: Breaking 6502 apart

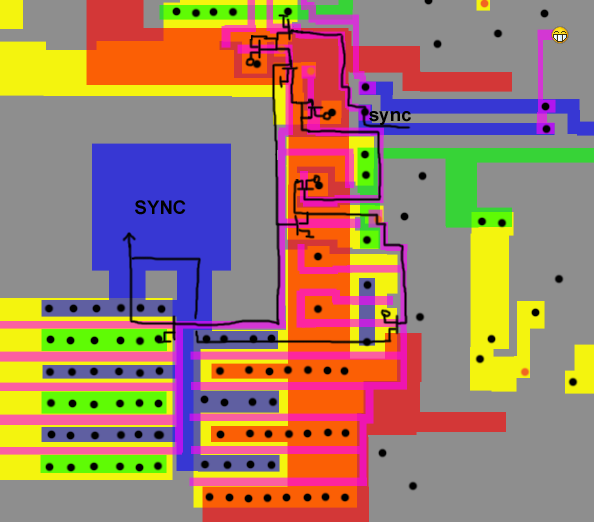

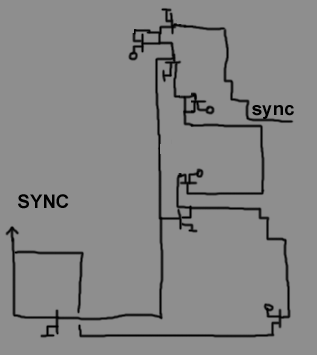

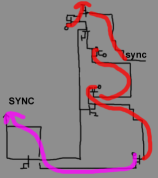

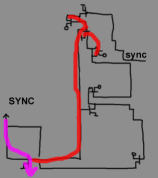

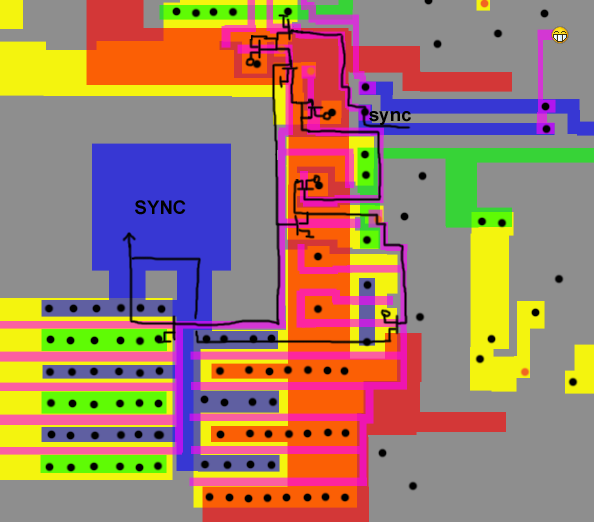

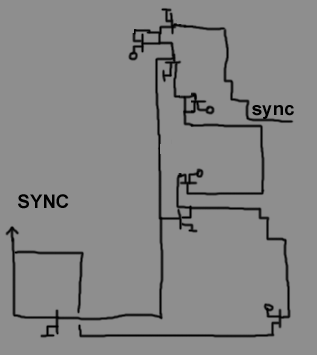

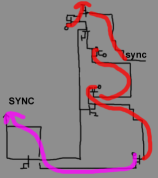

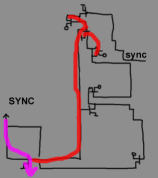

Todays speccy : SYNC

Color :

Transistor level :

Logic:

SYNC = sync (driven by internal signal through amplifiers)

Color :

Transistor level :

Logic:

SYNC = sync (driven by internal signal through amplifiers)

6502 addict

Re: Breaking 6502 apart

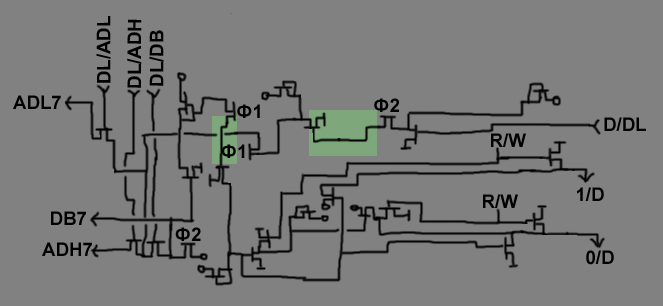

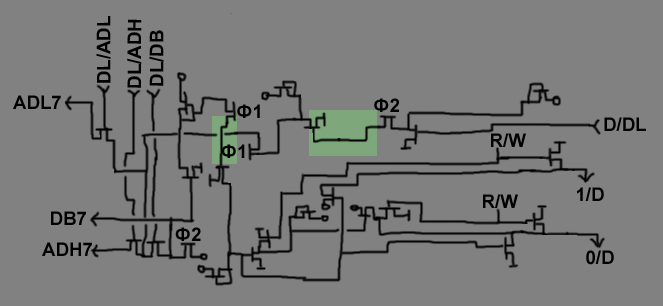

Found error in data latch (missing vias).

Updated transistor level schematics :

Updated transistor level schematics :

6502 addict

Re: Breaking 6502 apart

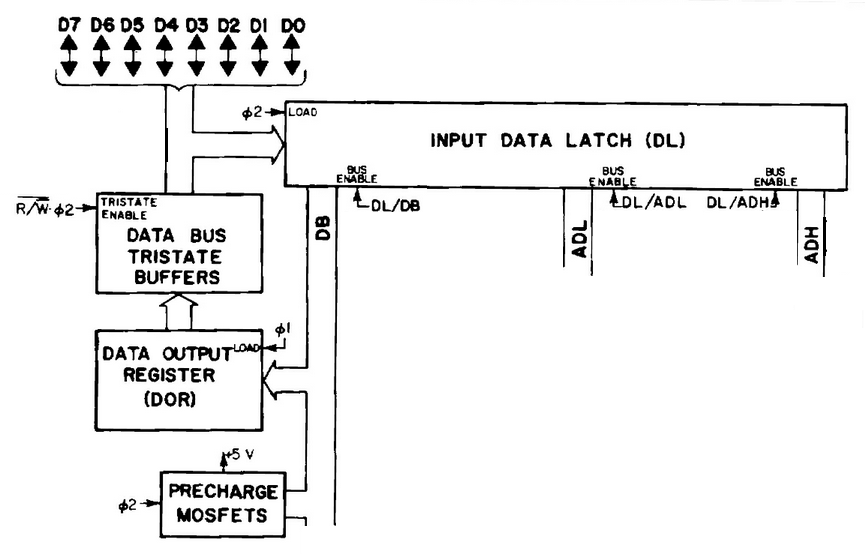

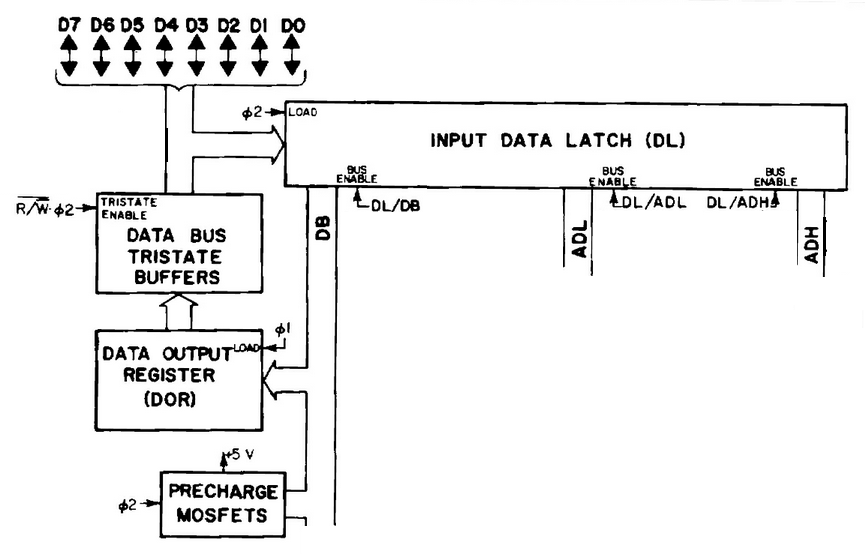

I completed reversing of data bus logic

Code: Select all

PHI1:

if (DL_ADL) ADL = DL;

if (DL_ADH) ADH = DL;

if (DL_DB) DB = DL;

DOR = DB;

PHI2:

if (RW == 0) DATA = DOR;

DL = DATA;

ADL = ADH = DB = 0xFF;

6502 addict

Re: Breaking 6502 apart

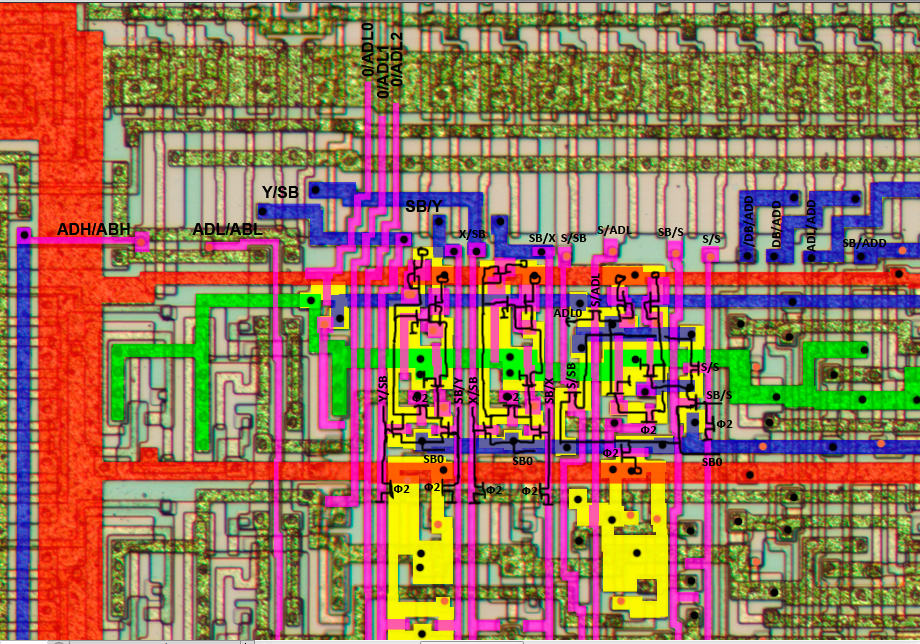

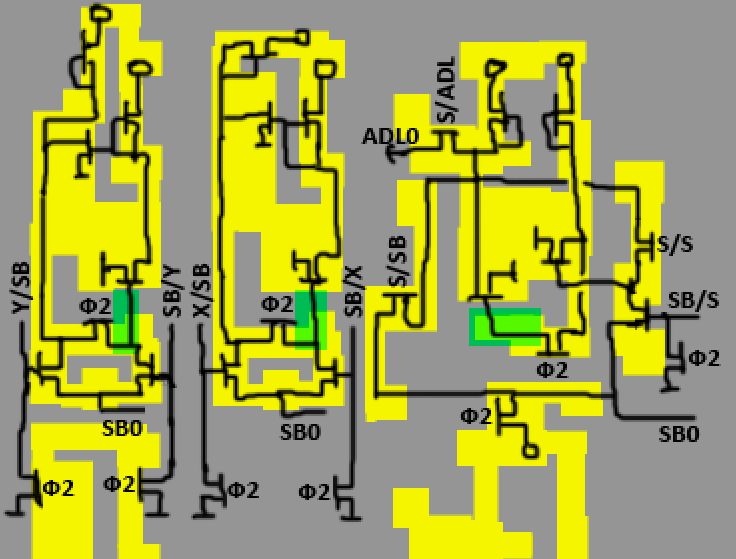

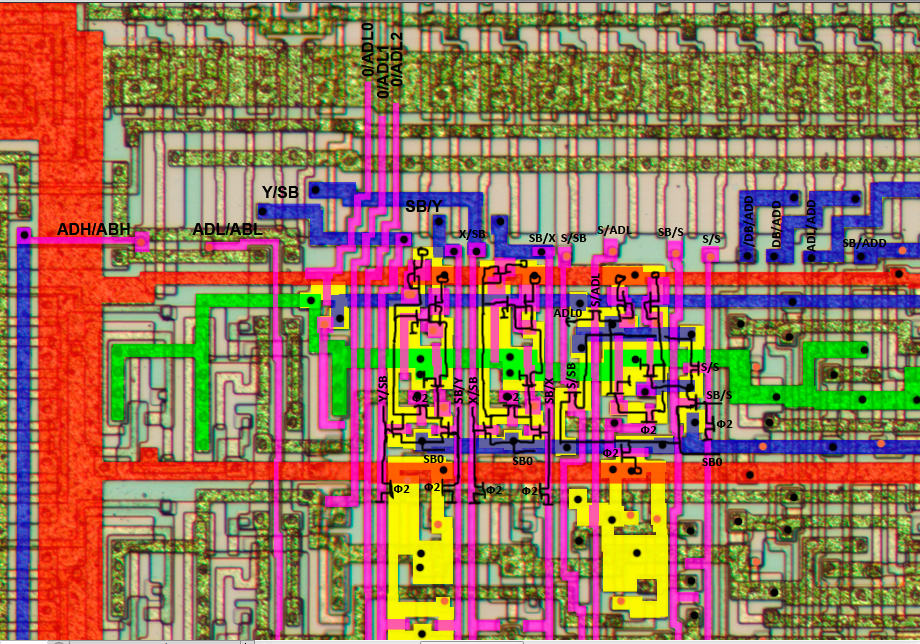

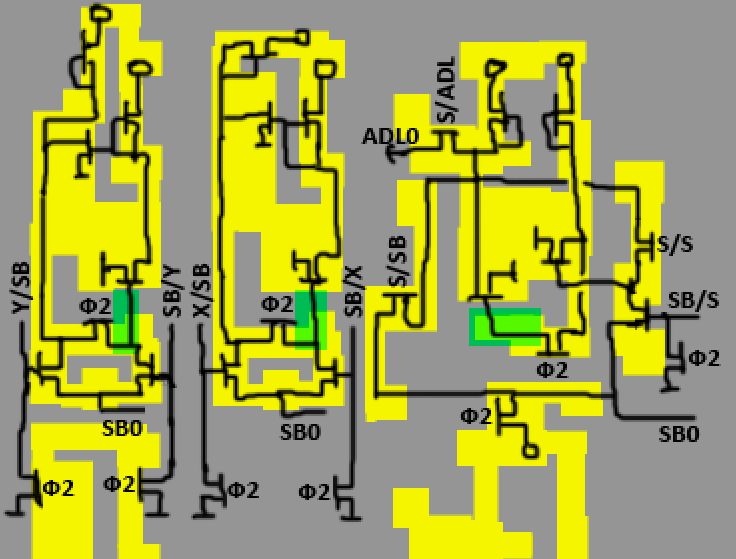

Todays speccy : Registers X, Y, S

Color (bit 0):

Transistor level:

Logic:

Color (bit 0):

Transistor level:

Logic:

Code: Select all

PHI1:

if ( Y/SB ) SB = Y;

if ( SB/Y ) Y = SB;

if ( X/SB ) SB = X;

if ( SB/X ) X = SB;

if ( S/ADL) ADL = S;

if ( S/SB ) SB = S;

if ( SB/S ) S = SB;

if ( S/S ) S = S;

PHI2:

SB = 0xFF;

6502 addict

Re: Breaking 6502 apart

Instantly recognisable! You notice how the first transistors from the databus are huge? I think that's to make the inverter's logic threshold a bit lower, which it needs to be because the databus is at TTL levels. Fortunately, it makes no difference to a logic sim. A big pulldown is a more eager one, so the output flips at a lower input voltage than it otherwise would.

You see the same thing in the next gate, after phi2, because the pass transistor transmits a degraded logic 1. The ClearIR inputs are normal sized by comparison. (As discussed previously, those PDn nodes are storage nodes.)

Cheers

Ed

You see the same thing in the next gate, after phi2, because the pass transistor transmits a degraded logic 1. The ClearIR inputs are normal sized by comparison. (As discussed previously, those PDn nodes are storage nodes.)

Cheers

Ed