Code: Select all

Broken external image

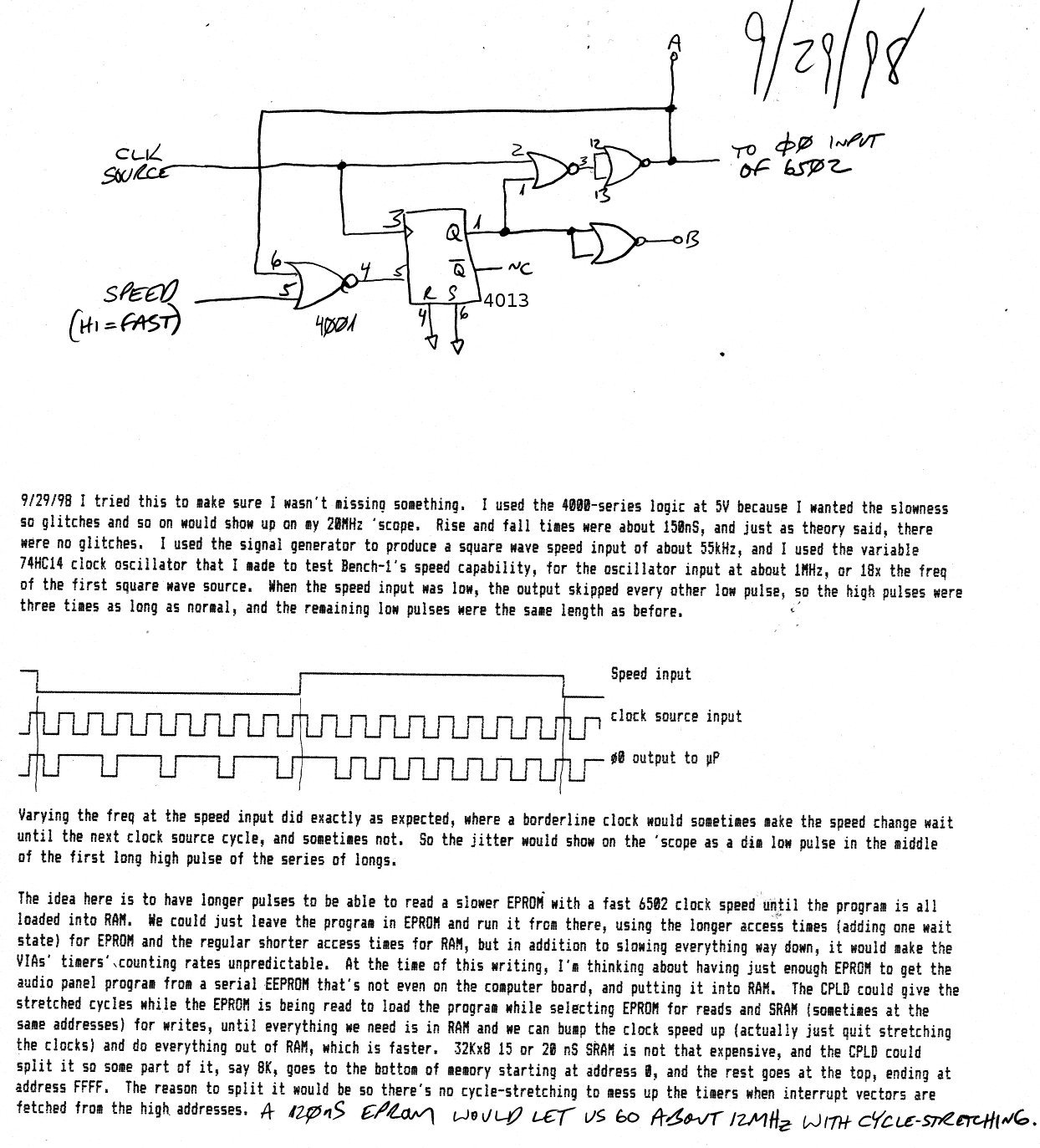

http://www.falvotech.com/tmp/whiteboard-1.jpgHISTORICAL NOTE: This will not work with NMOS 6502s. RDY is sampled during phase 1 on these CPUs, which is one of the reasons it was rarely used (it required fast address decoders). CMOS versions are required for this to work.

Code: Select all

Broken external image

http://www.falvotech.com/tmp/whiteboard-2.jpgThe circuit is a Johnson ring counter used to keep track of which cycle of the transaction it's in. We use a Johnson counter because it allows us to effortlessly detect back-to-back accesses to the same (slow) address space. Using a different counter would result in a slow first access, but then all subsequent burst accesses would run at bus rate, which isn't what you want.

SLOW is a signal derived from address decoding. It qualifies Phase-2 -- we don't want this circuit running when we're not accessing the slow resource. For as long as SLOW remains asserted and we have a valid clock, the counter will count. The inverter and OR gate ensure RDY remains pegged high when we're not accessing the slow device as well. That way, we don't lock up the bus.

Notice, though, that the XOR gate is used to derive the RDY signal. It's high if, and only if, we reach the end of the long cycle.

INTERESTING NOTE: The above circuit is actually a 68000 DTACK# generator, suitably modified to account for the 6502/65816's inability to distinguish one valid bus cycle from another.

Code: Select all

Broken external image

http://www.falvotech.com/tmp/whiteboard-3.jpgLet me know if this helps explain the idea better.