... Adrian's post made me stop and ask: "If I can use a '540 to do the inversion before latching the result then

why must I wait until PHI2 high before beginning address decoding?"

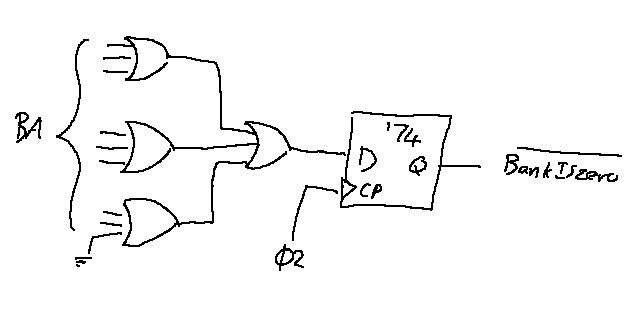

Let's say I'm doing some combinatorial logic on the Bank and Address lines. And I want to know if the bank address is zero - I can use four triple or gates wired together to detect 8 bit zero (active low). As long as the result is valid and latched before PHI2 goes high then I have practically

no propagation delay after PHI2 goes high. The work is already done and latched.

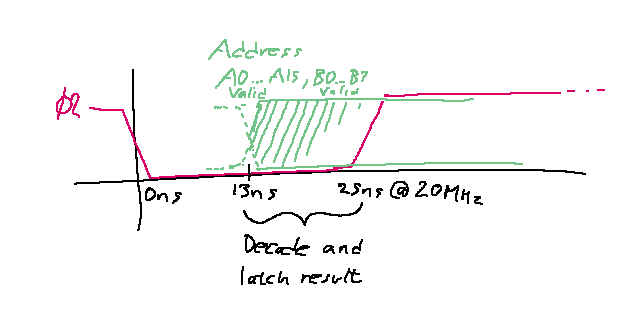

If we assume a I'm using a W65C816S6TQG-14 with VDD at 5V and with a 20Mhz clock.

- Address Predecode.png (10.41 KiB) Viewed 8875 times

then I have measured that the address lines become valid after 10 to 11ns. And the bank address lines become valid maybe a bit before 13ns*. This gives around 12ns to do address 'predecoding' and I think in systems with fast clocks that could be quite useful.

- Bank is Zero Latch.png (9.53 KiB) Viewed 8875 times

If I use four 74LVC1G332s with VCC at 5V and latch their result into a 74LVC1G79 also with VCC at 5V then I get a total propagation delay across that little circuit of 1.6ns + 1.6ns + 1.6ns. Let's just call it 5ns. And that fits easily in the 12ns I had remaining (25 - 13).

Of course after thinking I was really smart to have worked this out I clicked that this is probably

the method that 6502 systems have used to deal with address decoding and chip selection since their have been 6502 systems. And probably a lot of 65816 systems too; the WDC suggested circuit just constantly latches the bank address while PHI2 is low. It's only the Bank-Address-is-disappearing restriction in my head that made me think I should only start doing address decoding after PHI2 has gone high and after the '573** has stopped latching.

*

Judged by looking at failures at higher clock speeds. The datalines are too chatty for me to actually measure.

**

[Edit] Updated '574 to '573. Brainfart or finger trouble but I should have typed '573. Thanks to Garth for spotting that.