7a) PA,PB registers

It looks pretty similar to what we already had in the 6530.

RST active asynchronously clears all of the Bits in the registers

ORA, ORB, DDRA, DDRB.

Register section for PA0..PA7 looks pretty identical,

register section for PB0..PB6 looks pretty identical,

so we just focus on the circuitry for the PA0 and PB0 registers.

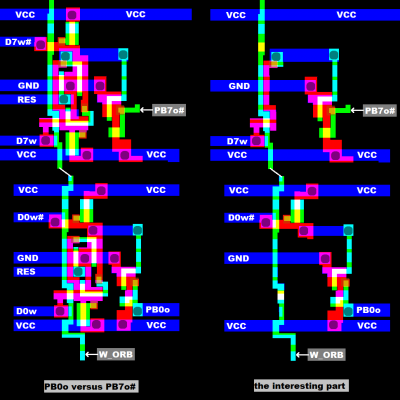

PB7 register circuitry is just a variation of PB0..6 register circuitry,

emitting a low_active PB7o# signal instead of a high_active PB7o signal.

;---

IRA: PA data input register

High_active control signal R_IRA connects/switches the output of an inverter

to the D0r internal data bus signal during PHI1=0 (wich is different from PHI2=1).

The inverter is fed with the PA0i# signal generated in "5) PA0",

and that's all there is to it.

;---

ORA: PA data output register

We have a fully static RS flipflop working as the ORA0 register Bit.

The internal write data bus signals D0w (high_active) and D0w# (low_active)

are used to set/clear the register Bit by high active control signal W_ORA during PHI0=0.

A NOR gate fed by ORA0 and DDRA0# generates PA0o#.

;

If data register ORA=0, and PA direction is set as output by DDRA0=1,

PA0o# is high, so the output driver switches PA0 to GND.

;---

DDRA: PA direction register //0=input, 1=output

We have a fully static RS flipflop working as the DDRA register Bit.

The internal write data bus signals D0w (high_active) and D0w# (low_active)

are used to set/clear the register Bit by high active control signal W_DDRA during PHI0=0.

High_active read control signal R_DDRA connects/switches the output of the RS flipflop

to the internal D0r read data bus line during PHI1=0.

;===

IRB: PB data input register

High_active control signal R_IRB connects/switches the output of an inverter

to the D0r internal data bus signal during PHI1=0 (wich is different from PHI2=1).

The inverter is fed with the PB0i# signal generated in "6a) PB0",

and that's all there is to it.

;---

ORB PB data output register

We have a fully static RS flipflop working as the ORB0 register Bit.

The internal write data bus signals D0w (high_active) and D0w# (low_active)

are used to set/clear the register Bit by high active control signal W_ORB during PHI0=0.

The buffered output of the RS flipflop is PB0o.

;---

DDRB: PB direction register //0=input, 1=output

We have a fully static RS flipflop working as the DDRB register Bit.

The internal write data bus signals D0w (high_active) and D0w# (low_active)

are used to set/clear the register Bit by high active control signal W_DDRB during PHI0=0.

The buffered output of the RS flipflop is PB0_DIR.

High_active read control signal R_DDRB connects/switches the buffered output of the RS flipflop

to the internal D0r read data bus line during PHI1=0.

;===

Of course I'm simplifying things, because the RS flipflops are not built from two NOR gates,

they are built from two "open collector" inverters which have pullups to VCC at the outputs.

This trick makes the RS flipflops smaller than when using NOR gates.

For RS flipflops built like this, R# is identical to Q, and S# is identical to Q#.

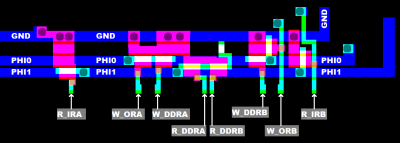

Read/write control signals enter the register block from the South.

North from the register block, we have FETs controlled by the clock signals,

switching the other end of every control signal to GND in the right moment,

to make sure that the control signals are inactive when they are supposed to be.

For every register in the 6522 it's implemented like this,

and we have seen that trick quite often in other MOS 65xx peripheral chips.

Attachment:

si6522_7_pa_pb_regs.png [ 59.22 KiB | Viewed 2192 times ]

si6522_7_pa_pb_regs.png [ 59.22 KiB | Viewed 2192 times ]

Attachment:

si6522_7_pa_pb_regs_north.png [ 21.41 KiB | Viewed 2192 times ]

si6522_7_pa_pb_regs_north.png [ 21.41 KiB | Viewed 2192 times ]

Attachment:

si6522_7_pb7_reg.png [ 34.7 KiB | Viewed 2192 times ]

si6522_7_pb7_reg.png [ 34.7 KiB | Viewed 2192 times ]

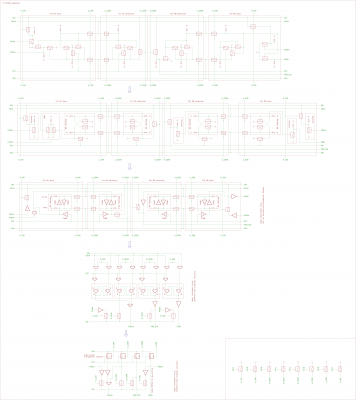

Attachment:

6522_7_pa_pb_regs.png [ 155.35 KiB | Viewed 2192 times ]

6522_7_pa_pb_regs.png [ 155.35 KiB | Viewed 2192 times ]

;---

Like in the 6530, when the 6502 reads data from the I\O ports,

it reads directly what's on the PA0..7 and PB0..7 pads.

To be more specific:

If PA\PB are configurated as inputs, and if PA\PB latching is disabled, the 6502 "directly" reads what's on the PA\PB pads.

In this case: if there is a spike on the PA\PB inputs during PHI2 while the 6502 is reading the PA\PB data input registers,

said spike is supposed to show up on the 6502 data bus during PHI2, and that's not good for signal integrity.

Maybe it would be better for signal integrity to sample the inputs from the pads

by transparent latches during PHI1=1, but then you need to make sure that the

"PA input latch" and "PB input latch" circuitry stays somewhat cycle/timing compatible to the original.