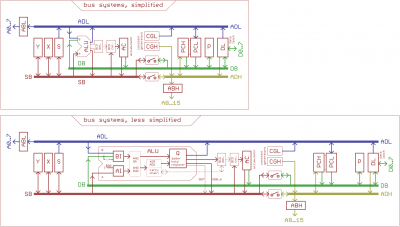

I admit that I was in a hurry when drawing the block diagram with the bus systems,

it was the last step of the dissection.

It isn't exactly a data path diagram, because it shows the data path plus the address path.

Block diagram intentionally was kept as simply as possible to give an overview.

Don't worry, I'm adding a more detailed version.

Quote:

- Missing S and ADL connection (S/ADL)

My mistake, fixed.

Quote:

- The fact of loading direct and inverse value to the BI ALU latch is not reflected (DB/ADD, NDB/ADD)

- Zero load command is not displayed on the AI latch (0/ADD)

I consider the AI and BI latches (plus the related circuitry) to be integral part of the ALU.

Quote:

- ADL/ADD connects ADL and BI (not AI)

My mistake, fixed.

Quote:

- Current value refresh commands are not displayed (S/S, PCL/PCL, PCH/PCH)

I consider the refresh paths to be integral part of the registers.

Quote:

- Instead of "BCD-detect" made ADD (Adder Hold) and output to ADL and SB buses from it

I consider the 'adder hold register' to be integral part of the ALU.

Quote:

- A -> AC (not to be confused with A Input)

In Hanson's block diagram, the accumulator is labeled 'AC', so I'm changing 'A' to 'AC'.

Quote:

- CGH and CGL are mixed up

Dang. How could this happen ?

My mistake, fixed.

Attachment:

6509_core_bus.png [ 71.03 KiB | Viewed 565 times ]

6509_core_bus.png [ 71.03 KiB | Viewed 565 times ]