I finally finished a schematic which I'm excited to share. Apologies in advance for the long post. I've tried to provide a thorough overview to try to make this as easy as possible to follow even for relative beginners like myself.

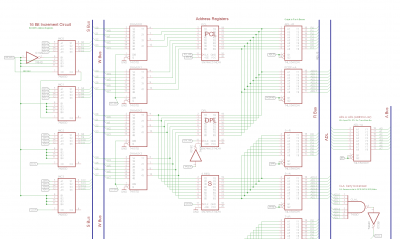

The schematic attached is for the CPU registers and associated logic. You might note the complete absence of 74CBT3245 ICs in the schematic. In the end, I felt I had not made very good use of these chips after all and decided instead to share the design as it was before, leaving in place unidirectional busses and the ICs I had selected previously. No doubt it will make sense to revisit this but I'll press on for now and learn as we go.

Looking at the schematic attached, the data path reflects the block diagram fairly closely and has the registers between the W Bus on the left and R Bus on the right. Each register is a 74HC574 with an “R” signal to output-enable them and a “WR” signal to clock them. To the right are the address registers (PCL/PCH, DPL/DPH, SP and T). Their outputs can be routed to the R Bus or to the the internal address bus “ADL/ADH”. Similarly, their inputs can come from the W Bus or the S Bus. The S Bus is the output of the INC16 circuit. See below.

Attachment:

Address Registers.png [ 148.53 KiB | Viewed 3208 times ]

Address Registers.png [ 148.53 KiB | Viewed 3208 times ]

On the far right are a pair of Carry Look Ahead NAND gates which feed the four 74HC283 INC16 adders. Addresses move from ADL/ADH to the external Address bus (“A Bus”) via /BE controlled 74HC541 buffers. In addition, the /ADHS.A signal sets the high-byte of the address to either ADH or a fixed value of $00, $01 or $FF depending on the address mode (ZDP, SP, FDP respectively).

DPH can be loaded directly from the external Data Bus by “DPH.LD” but it's not connected to the S Bus. Incrementing DP in fact only increments the lower 8 bits in DPL. The consequence is that DP will “warp-around” the same page if a page boundary is crossed when resolving the high-byte of an indirect address. This is also the NMOS 6502 behaviour.

IR is also loaded in parallel from the Data Bus during Fetch-Opcode operations ("IR.LD" selects that), or from the W Bus during interrupt processing. IR outputs directly to the Opcode lines (OP0 - OP7) which in turn feed the Control ROMs. The “INT” control signal is high during the first cycle of interrupt processing and thereby forces the Opcode to zero through the OP.LOGIC0 buffer.

The final item on the data path is the “R->DB" 74HC541 buffer which connects the R Bus to the external Data Bus for memory write operations. /MEM.W and /BE signals together enable this buffer for the full write-cycle.

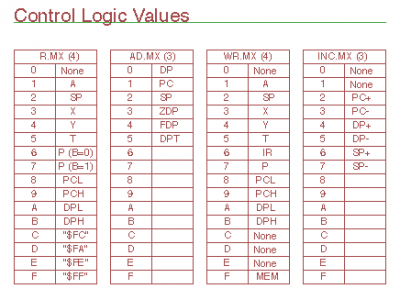

The control circuitry is driven by two Control ROMs. Each ROM is addressed by a 3-bit “Q” state, the current 8-bit Opcode and an INT control flag. Each of the 256 possible opcodes therefore has up to 8 micro-instructions (Q values 0 to 7). The output from these ROMs is decoded to produce all the control signals according to the following table:

Attachment:

control table.png [ 14.23 KiB | Viewed 3208 times ]

control table.png [ 14.23 KiB | Viewed 3208 times ]

- R.MX (4 bits) selects the register to read from and various constants on the R bus. The P register can be read either with a “0” or “1” in the “B” flag.

- AD.MX selects the address register being used to drive ADL/ADH: DP, PC, SP ($01/SP), ZDP ($00/DPL), FDP ($FF/DPL), and DPT (DPH/T).

- WR.MX (4 bits) selects the register to write to. $F selects external memory (decoded as "MEM.W").

- INC.MX controls the INC16 circuit and selects which register will receive the result.

- IR.LD and DPH.LD are taken directly from the control ROMs without decoding

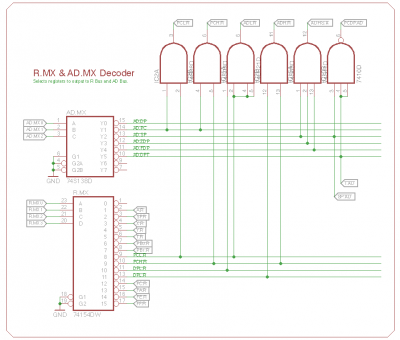

Each set of MX signals has an associated decoder to break out individual control lines and apply further logic where needed. R.MX and AD.MX produce "R" and "AD" signals as follows:

Attachment:

RMX.png [ 41.18 KiB | Viewed 3208 times ]

RMX.png [ 41.18 KiB | Viewed 3208 times ]

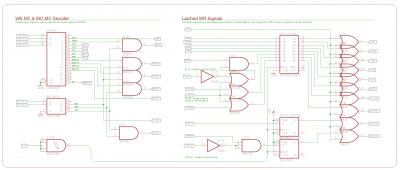

WR.MX and INC.MX are decoded into register-write signals (W signals) which need to be latched by WR.LATCH at the leading edge of phase 2 to prevent glitches and are further gated by /CLK to latch all registers with the trailing edge of phase 2. The memory write signal MEM.W, on the other hand, is clocked to take RW low for the duration of phase 2. PC.SW and DP.SW go to muxes and are left unlatched.

Attachment:

wrmx.png [ 94.36 KiB | Viewed 3208 times ]

wrmx.png [ 94.36 KiB | Viewed 3208 times ]

Some logic on the input to WR.LATCH deals with “parallel load” signals (IR.LD and DPH.LD) as well as the INHPF control signal coming from the ALU & CU card (“Inhibit Pre-Fetch” which prevents writing to the PC register and is needed during interrupt handling - more on that later).

Finally, there is also a 96 pin connector. My plan is to put this schematic on one “Registers” card connected to a backplane. I will need at least a second card for the ALU & CU, a third for memory and I/O and a final one for video.

Ok, that pretty much covers it. Now for some questions:

- Any tips to improve the schematics?

- Are there any obvious electrical problems evident, either with on-board or backplane connections?

- Are there more efficient ways to deal with the various addressing requirements (PC, DP, SP, ZDP, etc.)?

- I could use a wider control word and eliminate the MX decoding logic entirely. There are clear speed advantages to that, but as it stands, I am using 16 bits to encode 38 control signals. Any thoughts or suggestions with respect to this arrangement?

- I have left the busses active as Garth had suggested, using /BE to tri-state them under external control. Any issues now?

- I am using Schmitt-trigger gates for the clock signal. All other signals are taken from 96-pin header directly . Is that ok? Should off-board signals be buffered in some way?

Ok, that’s it for now. Many thanks to all for your comments and suggestions.

Best,

Drass