Hi everyone. Long time lurker, first time poster here.

I've been trying to design a 65C816 computer for a while now and I'm running into some issues that I think go beyond a mistaken connection. I've sent two versions of this computer in for fabrication. The first board didn't work at all. The second board does work, but is unstable under certain conditions. Anyways, I'm starting to think my ideas on the glue logic and address decoding is flawed. For example, if I upload a program to RAM that will never use the EEPROM, it will still activate the EEPROM (briefly). So, running programs within the RAM tends to be unstable.

Here's the link to the full KiCAD project:

https://github.com/halfburnttoast/TPC65_V3For the most part, I'm taking it right from the 65C816's datasheet, using a HC573 and HC245 to latch the bank address. One mistake I did make was to use two 74ALS00's instead of 74HC00's. I don't remember why I went with ALS chips, but I know now that the ALS->HC interface is incompatible and could be a source of the instability.

I've also been cross-referencing my computer with the schematic of WDC's 65C816 SBC and I noticed that they qualified the RAM and ROM's #OE as:

Code:

#OE = !(PHI2 & RWB)

I'm not completely sure why they went this is necessary if #WE overrides the #OE pin during writes, which is what I gathered from the datasheets. But, I'm suspecting that this is also an error on my part. I know I'm also not accounting for VDA and VPA. I'd like to try and include qualification for this by adding a third 74HC00. But, I'm paranoid that I'm overlooking some other aspect of the build.

My proposed memory map looks like:

Code:

0x000000 - 0x007FFF - BANK0 RAM

0x008000 - 0x00BFFF - IO

0x00C000 - 0x00FFFF - EEPROM

0x010000 + N - remaining banked RAM

To detect BANK0, I'm using a 74F521. But, I'm noticing on the oscilloscope that BANK0 is toggling even when running in emulation mode, which shouldn't happen. The HC573 is briefly latching an invalid value from the databus which, I'm suspecting, is related to it being driven by a ALS00. But, I'm not sure where the primary source of instability is coming from or if it's a constellation of instability.

So, rather than continue burning money on non-working boards, I'd like to see if there are glaring problems with my glue logic. From what I can tell, a lot of people who use the 65C816 use CPLDs as glue logic, but there aren't as many examples of jellybean logic gates, so I've mostly been taking notes from WDC's board. The clock source and serial interface is an Arduino Nano, which I've optimized to put out about a 2.28MHz clock signal. Any help would be appreciated! I can provide more details if needed.

Attachment:

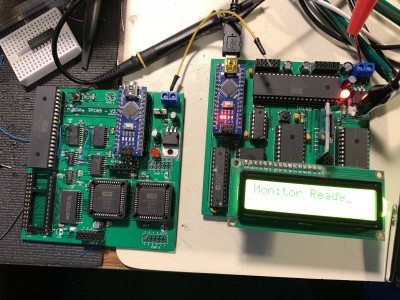

File comment: On right, my working 65C02 design. On left, working but unstable 65C816 board.

2020-12-04_17-23-09_IMG_7244.JPG [ 4.08 MiB | Viewed 1124 times ]

2020-12-04_17-23-09_IMG_7244.JPG [ 4.08 MiB | Viewed 1124 times ]