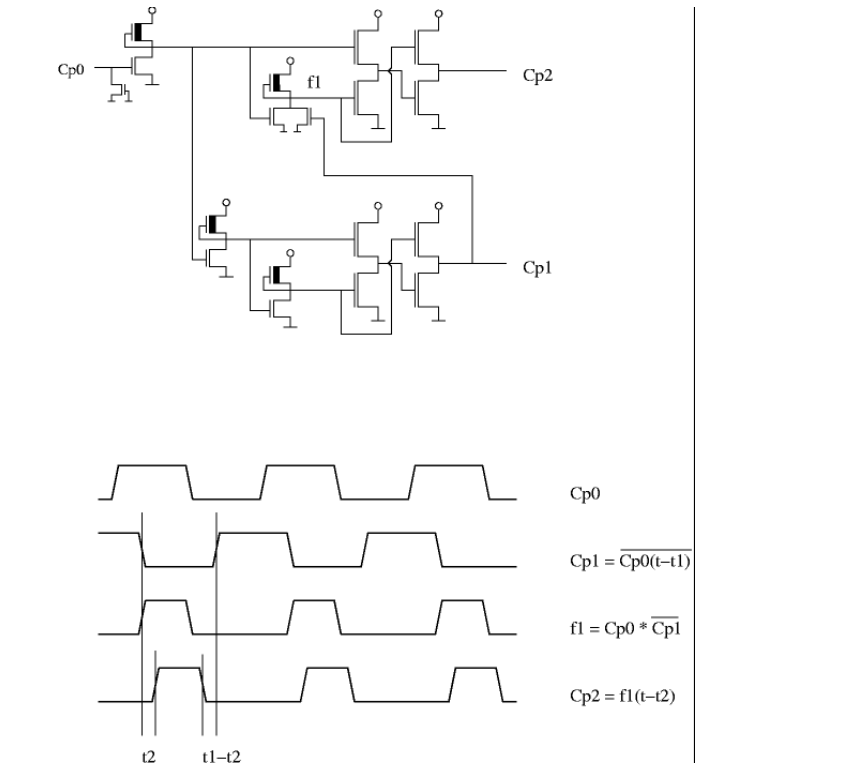

In the simulator I managed to figure out the following nodes:

cclk, cp1, clk0

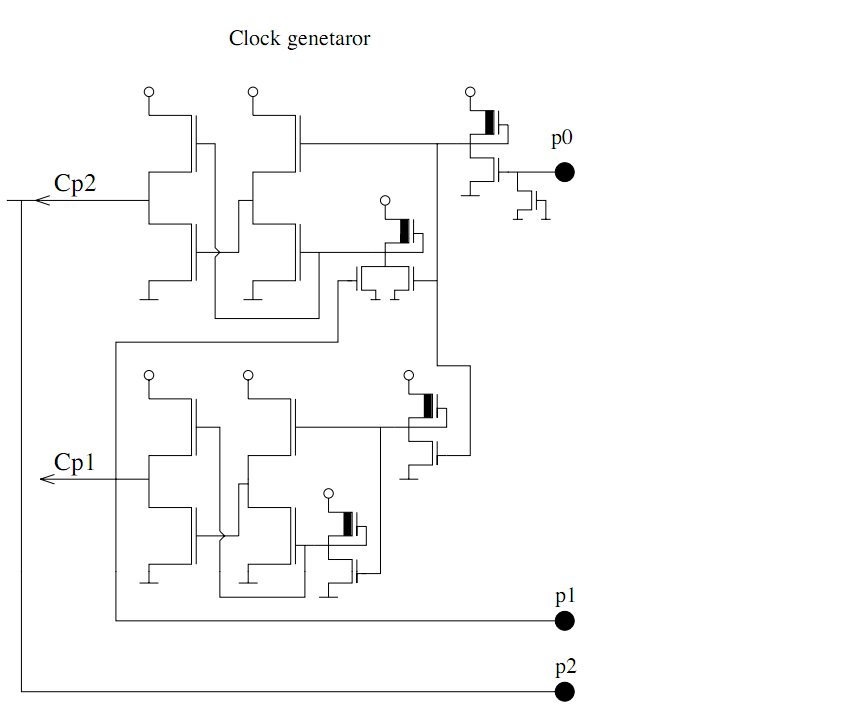

In the following schematic I see there is a clock generator which has

p0, p1, p2, Cp1, Cp2

This is part of the schematic that can be obtained from http://www.downloads.reactivemicro.com/ ... onics/CPU/.

Lastly, I hear people talking about phi1 and phi2 all the time. Is that the same as phase1 and phase2?

So my questions are:

1. How are cclk, cp1, clk0; p0, p1, p2, Cp1 Cp2; phi1 and phi2 related?

2. Where on the visual simulator is the clock generator located as detailed in the schematic? Notice that the schematic is turned 180° in relation to the visual simulator. I suspect the location is on the top almost at the right corner.