Page 1 of 2

Fast Mem accessed slowly

Posted: Fri Oct 31, 2025 3:50 pm

by richardc64

Has anyone experienced or heard of problems when accessing fast memory slowly? Such as 20-55nS sram being accessed with 500nS /CE?

Google and Bing Searches have only given me page after page of Stack -vs- Heap, registers -vs- files -vs- arrays - vs- database queries -vs- etc. Maybe I haven't asked correctly.

Thanks

Re: Fast Mem accessed slowly

Posted: Fri Oct 31, 2025 4:23 pm

by BigEd

One thing to watch: fast memories have complex internal sequences which trigger off changes to incoming signals. So you may want to be sure your address lines are stable before the chip begins an access. Look carefully at the timing diagrams.

Re: Fast Mem accessed slowly

Posted: Fri Oct 31, 2025 5:42 pm

by Yuri

Has anyone experienced or heard of problems when accessing fast memory slowly? Such as 20-55nS sram being accessed with 500nS /CE?

Google and Bing Searches have only given me page after page of Stack -vs- Heap, registers -vs- files -vs- arrays - vs- database queries -vs- etc. Maybe I haven't asked correctly.

Thanks

Are you wanting to know if you can use a 20-55ns SRAM while holding the /CE line low for 500+ns? If so, as far as I know there shouldn't be a problem with that so long as all the other lines also stable for that long as well.

(For that mater I have often just tied the /CE directly to ground for some circuits where I don't really need it.)

Re: Fast Mem accessed slowly

Posted: Fri Oct 31, 2025 6:39 pm

by BigDumbDinosaur

Has anyone experienced or heard of problems when accessing fast memory slowly? Such as 20-55nS sram being accessed with 500nS /CE?

SRAM means “static random-access memory.” The key word here is “static,” which means the RAM merely responds to input signal states (low or high), without regard to the passage of time. Ergo there should never be a problem with slow access, as long as you operate within the recommended DC specs, e.g., VIL, VIH, etc., observe the input setup and hold times, and input signal transition rates are within spec.

Re: Fast Mem accessed slowly

Posted: Fri Oct 31, 2025 8:22 pm

by gfoot

Google and Bing Searches have only given me page after page of Stack -vs- Heap, registers -vs- files -vs- arrays - vs- database queries -vs- etc. Maybe I haven't asked correctly.

These aren't really good places to look for this sort of information - the first and pretty much only place to look is the datasheet for whichever RAM module you're using - it should state any restrictions on access times, and if it doesn't say that there's a maximum duration for one of the signals to be in a certain state, and doesn't state anything like an overall maximum cycle time, then it should be fine to access it as slowly as you like. For typical static RAM, as stated above, it shouldn't be a problem.

Re: Fast Mem accessed slowly

Posted: Fri Oct 31, 2025 10:10 pm

by GARTHWILSON

Has anyone experienced or heard of problems when accessing fast memory slowly? Such as 20-55nS sram being accessed with 500nS /CE?

Re: Fast Mem accessed slowly

Posted: Fri Oct 31, 2025 10:53 pm

by BillO

I have a small SBC I created about a decade ago. It uses a W65C02 CPU, which is a static part and I use 10ns static ram and 45ns EEROM. The SRAM is the skinny dip SRAM they used to use for cache in 100MHz 486 mother boards. The slowest I've run that board at is down to 100Hz to troubleshoot some I/O board I was working on, and it ran just fine. We're talking a 10ms cycle time here. The moral of the story is, if the relative timing of the signals is correct, it will likely not be a problem. If you are having trouble, then check to make sure the relative timings of the address bus, data buss, R/W and /CE signals are correct.

Re: Fast Mem accessed slowly

Posted: Fri Oct 31, 2025 11:28 pm

by J64C

I have a small SBC I created about a decade ago. It uses a W65C02 CPU, which is a static part and I use 10ns static ram and 45ns EEROM. The SRAM is the skinny dip SRAM they used to use for cache in 100MHz 486 mother boards. The slowest I've run that board at is down to 100Hz to troubleshoot some I/O board I was working on, and it ran just fine. We're talking a 10ms cycle time here. The moral of the story is, if the relative timing of the signals is correct, it will likely not be a problem. If you are having trouble, then check to make sure the relative timings of the address bus, data buss, R/W and /CE signals are correct.

Same here. I run 12 ns RAM on one of my boards and it's happy to run anywhere between 40 MHz or indefinite single stepping (i.e. hours between clock cycles if need be).

Re: Fast Mem accessed slowly

Posted: Sat Nov 01, 2025 3:45 am

by richardc64

Reassuring responses, some verifying things I suspected, but wasn't sure of. Thanks.

(For that mater I have often just tied the /CE directly to ground for some circuits where I don't really need it.)

I've wondered about that, and how it relates to most devices' datasheets stating Write can be /WE controlled or /CE controlled.

Re: Fast Mem accessed slowly

Posted: Sat Nov 01, 2025 5:18 am

by BigDumbDinosaur

(For that mater I have often just tied the /CE directly to ground for some circuits where I don't really need it.)

My opinion is that is bad design practice. Yes, it will work, but there are potential timing problems with it and most SRAMs (and (E)EPROMs) will draw more current when /CS (/CE) is continuously asserted.

Best performance is usually achieved when writing is /WE controlled and /CS is asserted as soon as a valid address is generated by the MPU, which happens during Ø2 low. The data sheet’s timing specs will indicate if this is the case.

Similarly, best performance is usually achieved when reading is /OE controlled, again with /CS being asserted as soon as a valid address is generated. Qualifying /OE with Ø2 is optional with the 65C02 but mandatory with the 65C816 unless a bus transceiver is used and is put into the high-Z state during Ø2 low.

Re: Fast Mem accessed slowly

Posted: Sun Nov 02, 2025 4:24 am

by BillO

(For that mater I have often just tied the /CE directly to ground for some circuits where I don't really need it.)

My opinion is that is bad design practice. Yes, it will work, but there are potential timing problems with it and most SRAMs (and (E)EPROMs) will draw more current when /CS (/CE) is continuously asserted.

Best performance is usually achieved when writing is /WE controlled and /CS is asserted as soon as a valid address is generated by the MPU, which happens during Ø2 low. The data sheet’s timing specs will indicate if this is the case.

Similarly, best performance is usually achieved when reading is /OE controlled, again with /CS being asserted as soon as a valid address is generated. Qualifying /OE with Ø2 is optional with the 65C02 but mandatory with the 65C816 unless a bus transceiver is used and is put into the high-Z state during Ø2 low.

+1

Re: Fast Mem accessed slowly

Posted: Sun Nov 02, 2025 5:33 am

by Yuri

(For that mater I have often just tied the /CE directly to ground for some circuits where I don't really need it.)

My opinion is that is bad design practice. Yes, it will work, but there are potential timing problems with it and most SRAMs (and (E)EPROMs) will draw more current when /CS (/CE) is continuously asserted.

Best performance is usually achieved when writing is /WE controlled and /CS is asserted as soon as a valid address is generated by the MPU, which happens during Ø2 low. The data sheet’s timing specs will indicate if this is the case.

Similarly, best performance is usually achieved when reading is /OE controlled, again with /CS being asserted as soon as a valid address is generated. Qualifying /OE with Ø2 is optional with the 65C02 but mandatory with the 65C816 unless a bus transceiver is used and is put into the high-Z state during Ø2 low.

In this context I'm talking about my VGA circuit where there address bus is only hooked up to the RAM and nothing else, there is no other device selection occurring, and every address change is completely intended for it and it alone, and it will never not be accessed in favor of something else.

No doubt there is some timing considerations there though; but in this instance I think what I'm doing is "okay"

For a more complex circuit like putting RAM on the 6502 bus with so many other devices I absolutely agree, use the /CE line, it just gives much finer control.

But to the OP's question, if you want to hold /CE low for many more nanoseconds longer than the spec of the SRAM (e.g. single stepping a 65C02, or using it at a clock frequency much lower than it's rating), then I think my point still stands. It should be fine; it shouldn't lose its contents like DRAM does, and will not cause any ill effects like releasing the magic smoke.

Of course, as most have already pointed out, read the data sheet (thoroughly) to be absolutely sure for the make/model of RAM your using.

Re: Fast Mem accessed slowly

Posted: Sun Nov 02, 2025 8:33 pm

by fachat

Has anyone experienced or heard of problems when accessing fast memory slowly? Such as 20-55nS sram being accessed with 500nS /CE?

SRAM means “static random-access memory.” The key word here is “static,” which means the RAM merely responds to input signal states (low or high), without regard to the passage of time. Ergo there should never be a problem with slow access, as long as you operate within the recommended DC specs, e.g., VIL, VIH, etc., observe the input setup and hold times, and input signal transition rates are within spec.

I'm not sure if that is true today, but I remember some pseudo static RAM being declared as SRAM that may invalidate that assumption.

It's best to look at the datasheet and see if there is an upper limit noted.

André

Re: Fast Mem accessed slowly

Posted: Sun Nov 02, 2025 9:54 pm

by BigDumbDinosaur

Has anyone experienced or heard of problems when accessing fast memory slowly? Such as 20-55nS sram being accessed with 500nS /CE?

SRAM means “static random-access memory.” The key word here is “static,” which means the RAM merely responds to input signal states (low or high), without regard to the passage of time. Ergo there should never be a problem with slow access, as long as you operate within the recommended DC specs, e.g., VIL, VIH, etc., observe the input setup and hold times, and input signal transition rates are within spec.

I'm not sure if that is true today, but I remember some pseudo static RAM being declared as SRAM that may invalidate that assumption.

It's best to look at the datasheet and see if there is an upper limit noted.

I did say that in my post.

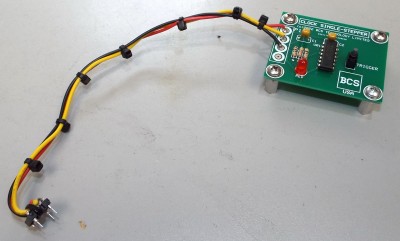

I have used several brands of SRAM in my contraptions and have, at times, used the clock stepper gadget to single-step a program. In one case, I was working on that when I got called away and was not able to return to what I was working on for several days. When I did get back on it, things continued without an issue. In other words, the SRAM (and the 65C816) was truly static.

- Clock Stepper Gadget

Re: Fast Mem accessed slowly

Posted: Mon Nov 03, 2025 8:31 am

by fachat

Yes of course SRAM means static.

Just I remembered that there was PSRAM at some time. E.g.

https://www.alldatasheet.net/datasheet- ... 8512A.html

It's got a max CE pulse time of 10u.

But those are obsolet today I'd think

André