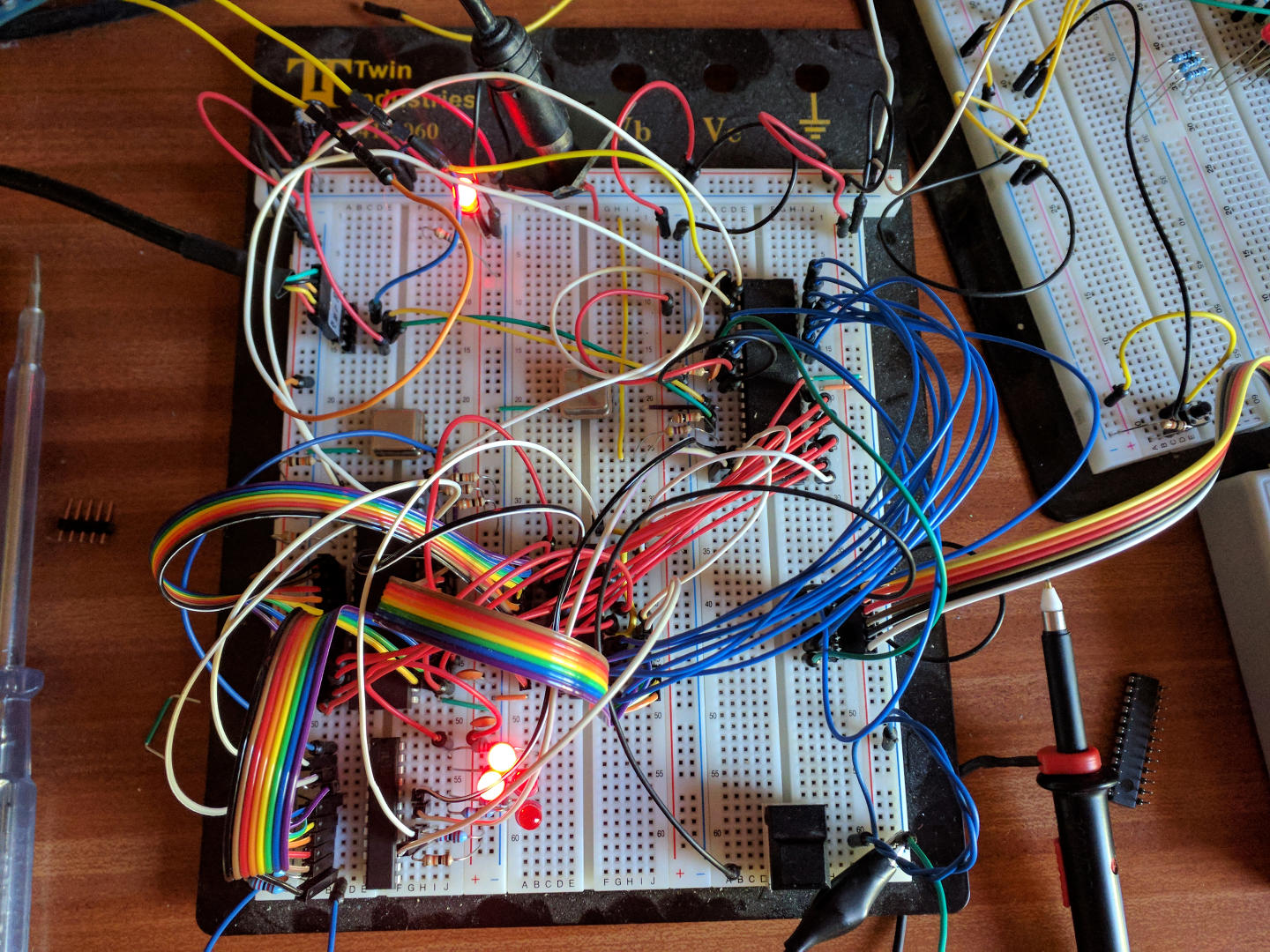

I cobbled it together on breadboards as a quick proof of concept, then put it on stripboard.

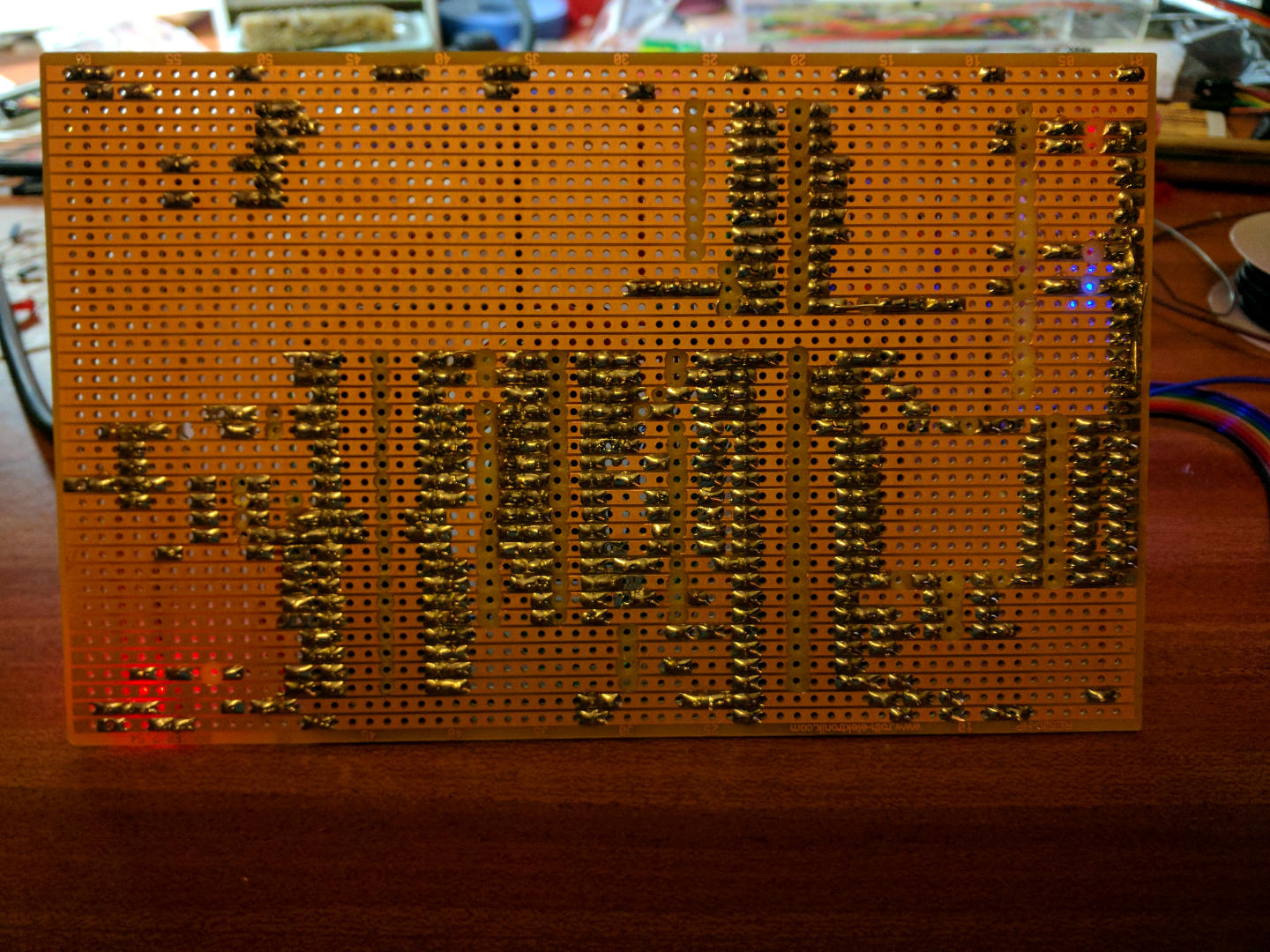

The Ugly Mess of wires!

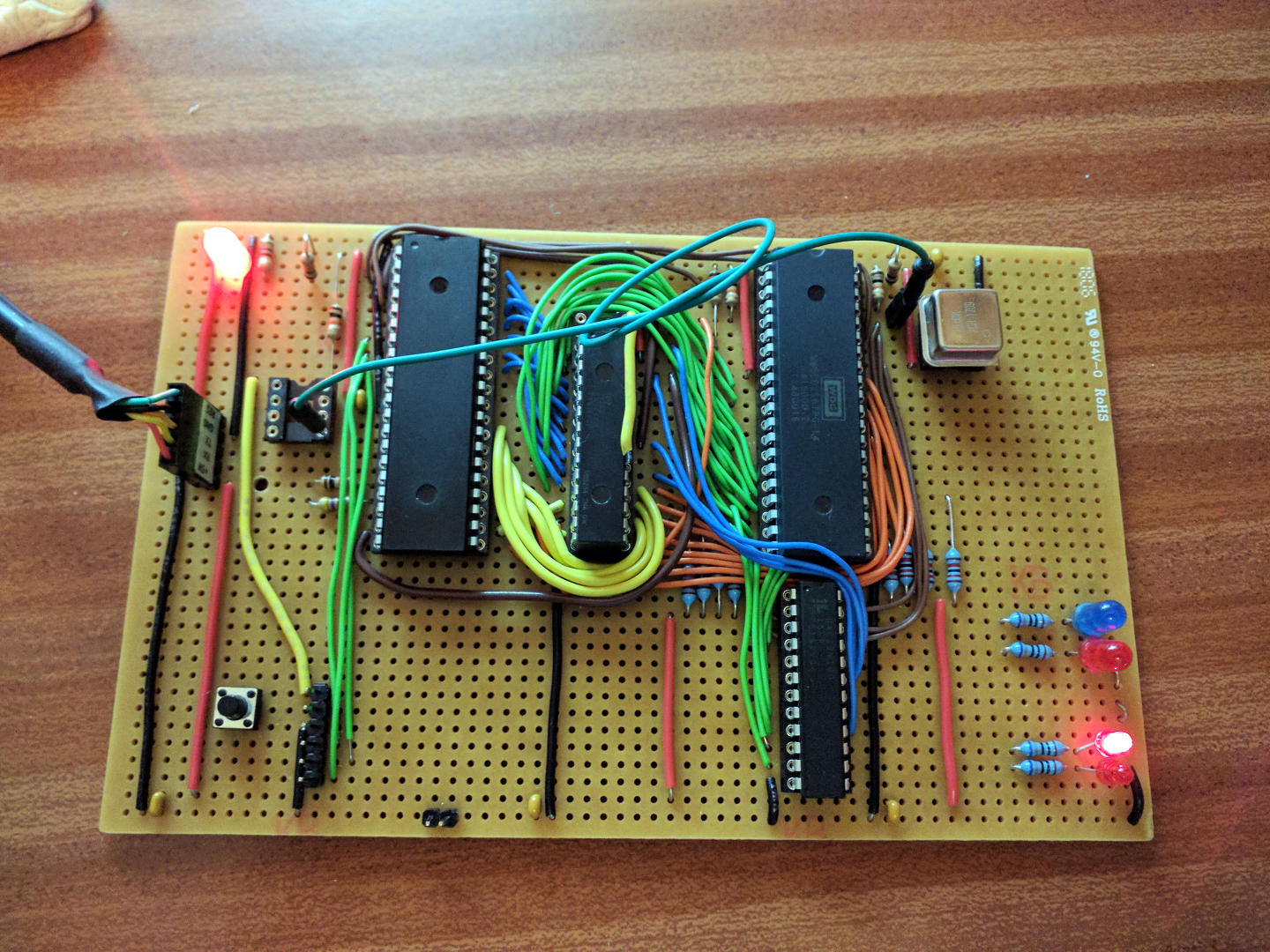

To give you an idea of the chips, from left to right: ATmega 1280p, 64KB RAM (2 x 32Kx8 stacked, yellow wire is the chip select from the top-one), and the 65c02 and below that is a Lattice GAL 22v10.

So no ROM - the ATmega pokes code into the top 256 bytes and can control the BE, Rdy, Reset and IRQ lines to the 6502. (It also reads the Rdy line which is the signal that the 6502 wants to send data to the ATmega. ATmega provides video 320x240x1 PAL composite), serial and soon SD card via SPI. I have 2 spare pins on the ATmega which I may use to implement a PS/2 keyboard interface.

The greenish floating wire is carrying the 16Mhz clock from the 6502 to the ATmega only because I only have one 16Mhz crystal osc. (yet another surprise that it works - it's probably bleeding 16Mhz all over the place, but it works!)

I started it at 2Mhz and was nicely surprised when it got to 16Mhz. It's ran an overnight memory test (250,000 passes) without any issues (the RAM is 12ns though)

The GAL decodes A15 for the 2 RAM chip selects and a page of IO at $FE00 (which the only thing connected to is that 5mm red LED) and qualifies read and write to the memory from the cpu + ph2 - the usual stuff.

I had intended to stick a 65c22 on it, but made a bit of an oops with the chip positioning and didn't leave quite enough room to the right, although I have seriously considered straightening the pins and mounting a 65c22 vertically, but I don't really need one for this experiment. I might stick a latch and some LEDs on it though.

So my plan is to play with this for a while, then make an '816 version then PCBs. (and invest in some "proper" 14Mhz crystal oscs!

Cheers,

-Gordon