Posted: Wed Oct 13, 2010 3:54 pm

Bidirectional buses are a PITA because they can violate timing constraints that synthesis languages depend on for correctness. Lots of loading and long lead lengths (even on chip) can result in unpredictable propagation delays.

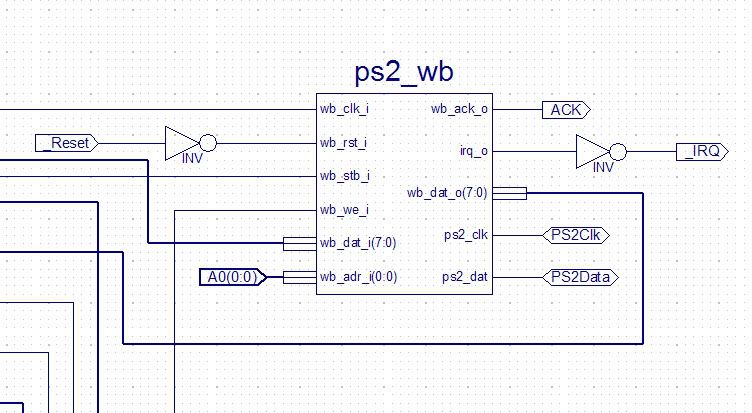

Separating the input and output buses allows you to use all point-to-point links, which are, at once, easier for the synthesis software to route, easier to analyze timing for, and absolutely guarantees a circuit where you cannot accidentally short something out. A "bus" is constructed by logically ORing (or, if active low, ANDing) the relevant signals. For example, if you were to replicate a Commodore 64, you'd form its backbone bus by ORing D0_CPU_O, D0_VIC_O, D0_SID_O, D0_CIA1_O, D0_CIA2_O, and D0_RAM_O to a single D0_BUS_I. That way, bus contention only yields incorrect results, never a short circuit, and you always know that the bus delay is a single gate (the OR gate). If I recall correctly, there is a great explanation of this in the Wishbone bus specifications.

Separating the input and output buses allows you to use all point-to-point links, which are, at once, easier for the synthesis software to route, easier to analyze timing for, and absolutely guarantees a circuit where you cannot accidentally short something out. A "bus" is constructed by logically ORing (or, if active low, ANDing) the relevant signals. For example, if you were to replicate a Commodore 64, you'd form its backbone bus by ORing D0_CPU_O, D0_VIC_O, D0_SID_O, D0_CIA1_O, D0_CIA2_O, and D0_RAM_O to a single D0_BUS_I. That way, bus contention only yields incorrect results, never a short circuit, and you always know that the bus delay is a single gate (the OR gate). If I recall correctly, there is a great explanation of this in the Wishbone bus specifications.