ElEctric_EyE, Any progress on your trouble?

Did you see the suggestions Lee and I gave?

If you can post a little more of the schematic (or a link to it), it would help.

Daryl

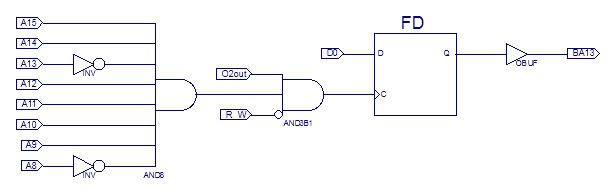

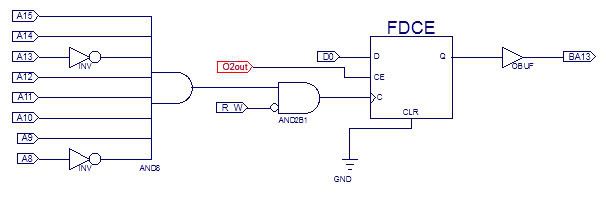

I have taken Leeeeee's suggestion to mirror the write-only register with a zero page register. The loop reads and writes to the zero page reg and then writes to the register inside the CPLD too, Doesn't work. In fact the 5 bit flip flop inside the CPLD is not being written to correctly, ever. I'm focusing now on this issue. The divider clocks in the CPLD are working fine... I've got the display to do a reset and clear. The bank circuit is not working. The previous schematic has only the flip flop (output/write to only), and phase 2 is also being used earlier in the logic path, instead of where it should be, at the very last stage of decoding. I've taken care of that as well in the next schematic, but it still isn't working. Before I start banging my head against the wall, I am going to start the latest schematic from scratch. I went through this process before and all of a sudden the circuit worked... A Xilinx software issue or maybe I'm closing down the software incorrectly...

From the schematic, it looks like a write to DExx loads the upper address bytes. Is this the "bank" variable referenced in your code?

...

Daryl

The 5 bit bank Reg is @ $DE00 and is mirrored through $DEFF. The 16K window the 65C02 sees (into 512K) is from $8000-$BFFF. In order for this part of my software to work correctly the bank Reg has to be #$00. I have the character fonts and character string data there (They used to be from $F000-$FFF9 on the 8K OS EEPROM.)

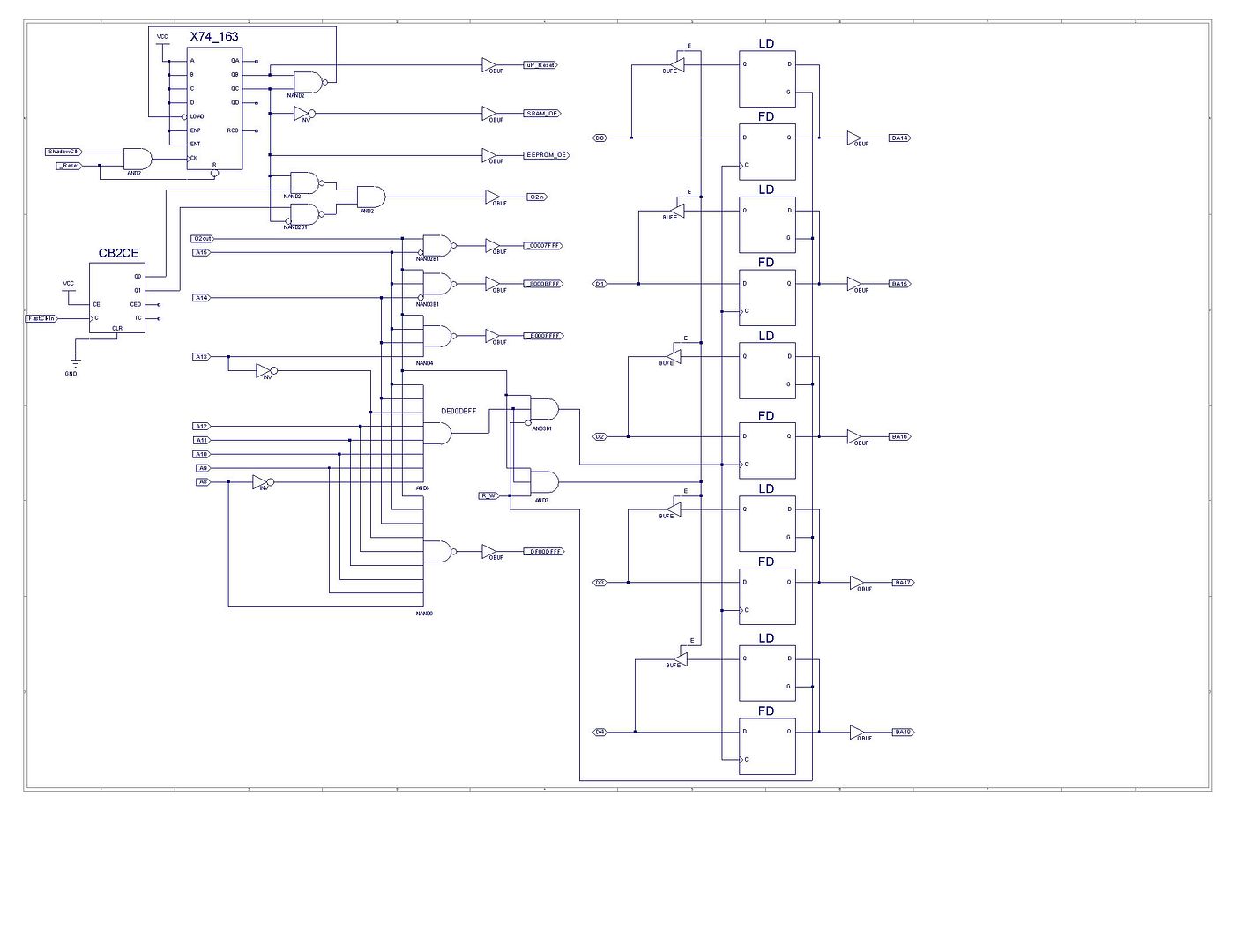

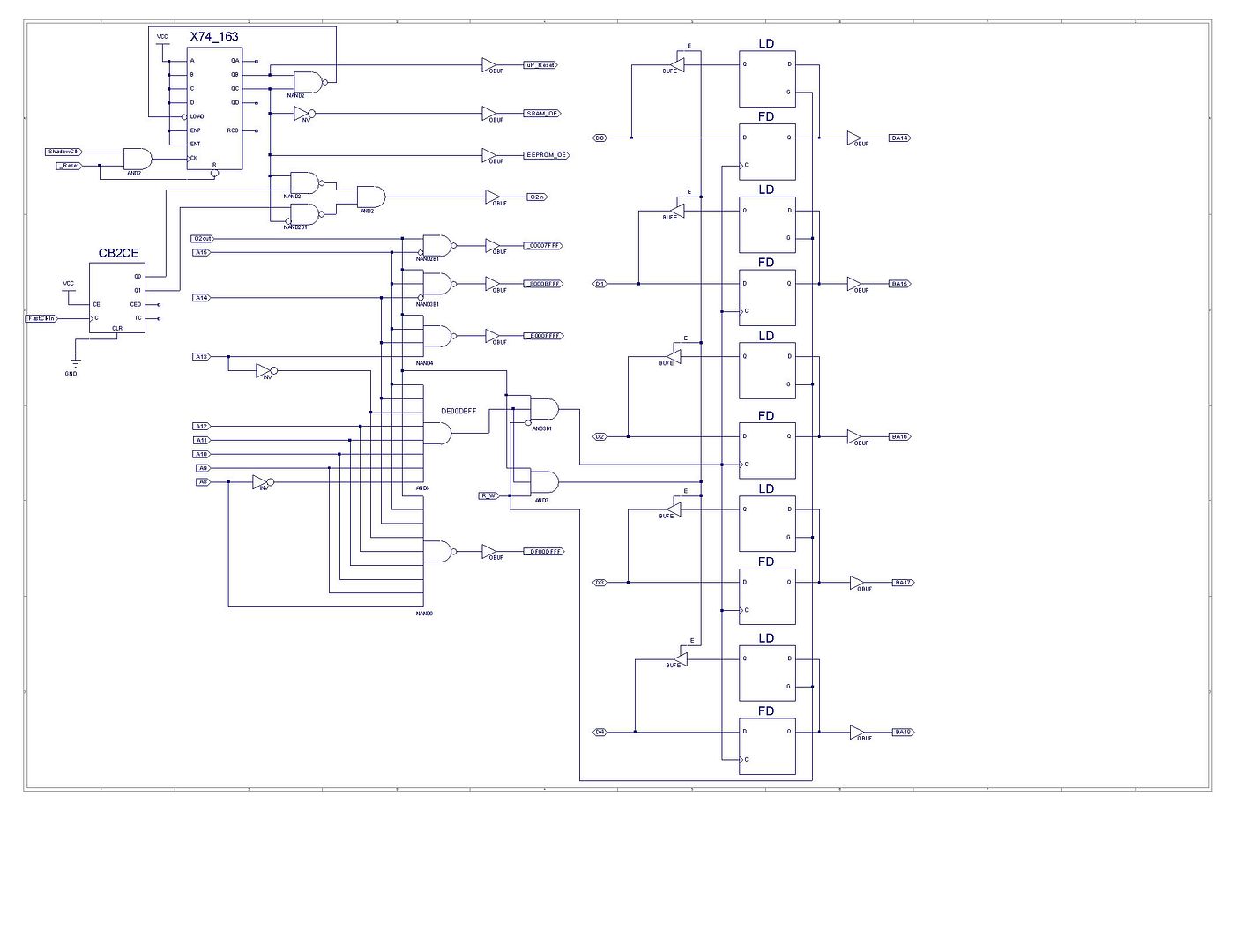

Here's the updated schematic (I am trying to use a new (.emf) format so the pic will fit into whatever size screen or CRT you are using).

Edit: The .emf format is not supported by photobucket, sorry for the large pic, but I am tired, soon off to bed. Thanks for the sugg's. I'll work on the pic size... In the schematic below "FD" is a D-type flip flop (like a 74374), and "LD" is a D-type latch (like a 74373), except the clock on "FD" latches the data on the rising edge, and the data on "LD" is transparent on a high "G". Also the tri-state BUFE's on the output of the "LD" latches are active high...

...Did not have a close look, but this looks like 8bit code to me. Did you try to put the X/Y registers in 16bit mode and use 24bit absolute address code? Makes such loops much simpler.

André

Sounds like the 65816? I have zero experience with that CPU, Andre. This is strictly WDC65C02 at this point.