BB816 Computer YouTube Series

- akohlbecker

- Posts: 282

- Joined: 24 Jul 2021

- Contact:

Re: 65C816 Computer YouTube Series

Episode 16 is out!

In this episode, I re-work the address decoding circuit. I'm pretty happy with the result: Gone is the obsolete 74HC4078, which I was able to replace thanks to the 74AC563 inverting latch. I can now detect bank zero using a (N)AND gate rather than a (N)OR.

Here is the new circuit I came up with, and as you can see I still meet the propagation constraints for my 4MHz frequency goal.

In this episode, I re-work the address decoding circuit. I'm pretty happy with the result: Gone is the obsolete 74HC4078, which I was able to replace thanks to the 74AC563 inverting latch. I can now detect bank zero using a (N)AND gate rather than a (N)OR.

Here is the new circuit I came up with, and as you can see I still meet the propagation constraints for my 4MHz frequency goal.

Re: 65C816 Computer YouTube Series

It’s neat to see test driven development of logic circuits, that’s a pretty good tool.

- akohlbecker

- Posts: 282

- Joined: 24 Jul 2021

- Contact:

Re: 65C816 Computer YouTube Series

If you enjoy it and would like to see more I can recommend rj45's channel, he is building a CPU and a VDP from scratch in Digital: https://www.youtube.com/c/rj45Creates

- akohlbecker

- Posts: 282

- Joined: 24 Jul 2021

- Contact:

Re: 65C816 Computer YouTube Series

Episode 17 is out!

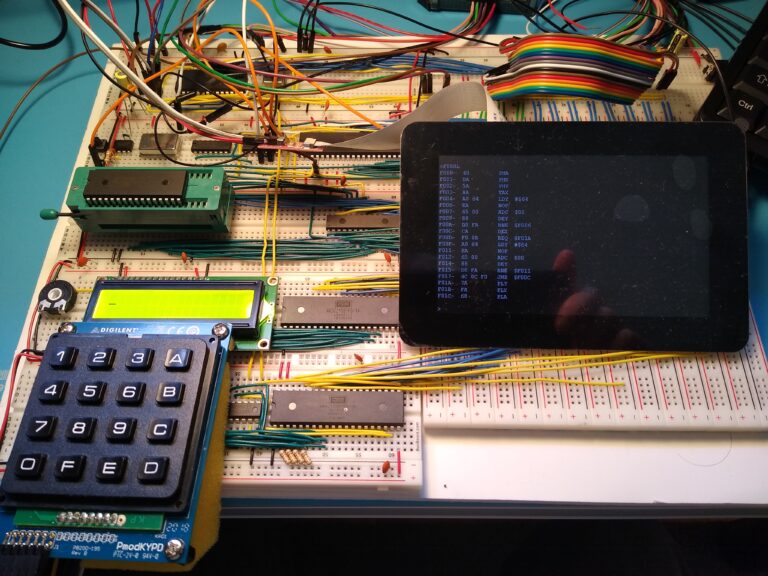

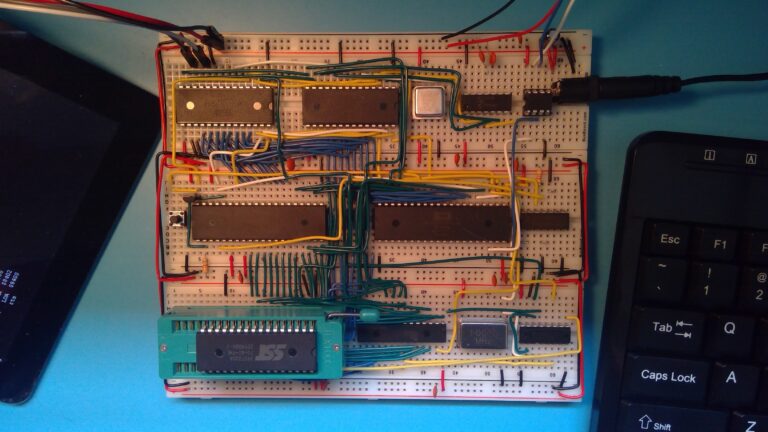

In this episode, I battle some signal integrity problems, as my memtest program is reporting bit flips on the data bus. I re-do my power delivery network and that seems to help a bit, but ultimately I think the length of my data bus and address bus wires is causing reflections, so the problem persists for now, albeit less frequent. Along the way, I add a Teensy bus monitor to help me see what's happening on the busses.

Hope you enjoy!

I'm considering moving to a backplane system, but I worry about how that is going to look on top-down video and how to integrate breadboard work on it. Looking at DIN 41612 connectors, or even PCIe x16 for better signal integrity (the former being specced up to 3MHz only apparently). I could go for PCIe cards, and use a PCIe ribbon extension to bring the signals to a breadboard?

Any feedback on this idea is welcome, as well as suggestions on how to fix my signal integrity problems on the current build

In this episode, I battle some signal integrity problems, as my memtest program is reporting bit flips on the data bus. I re-do my power delivery network and that seems to help a bit, but ultimately I think the length of my data bus and address bus wires is causing reflections, so the problem persists for now, albeit less frequent. Along the way, I add a Teensy bus monitor to help me see what's happening on the busses.

Hope you enjoy!

I'm considering moving to a backplane system, but I worry about how that is going to look on top-down video and how to integrate breadboard work on it. Looking at DIN 41612 connectors, or even PCIe x16 for better signal integrity (the former being specced up to 3MHz only apparently). I could go for PCIe cards, and use a PCIe ribbon extension to bring the signals to a breadboard?

Any feedback on this idea is welcome, as well as suggestions on how to fix my signal integrity problems on the current build

Re: 65C816 Computer YouTube Series

akohlbecker wrote:

suggestions on how to fix my signal integrity problems on the current build

Imagine Chip A in Location A. We know it outputs a signal whose current gets carried by a conductor to Chip B, some distance away. It's easy to forget that, in order to complete the circuit, a return current must flow through the Power & Ground Distribution network from Chip B back to Chip A.

The return current will follow the path of least inductance (the resistance is low enough not to matter). Inductance is the enemy, and we can minimize inductance by providing a return path that's in close proximity to the signal path. This is crucial. The signal current and return current flow in opposite directions, and when two opposing currents are in close proximity their magnetic fields tend to mutually cancel. And that's what we want, because it reduces inductance.

(BTW there's another way of discussing this effect. Sometimes in reference documents the signal and return path are described as forming a loop, with the goal being to reduce the loop area -- and thus the number of lines of magnetic flux contained by the loop. Closer proximity means less loop area. In turn we get fewer lines of magnetic flux passing through the loop, which results in less inductance.)

The Power & Ground Distribution Network can support this by making many paths available. For every signal wire connecting Chip A to Chip B there would ideally also be, in close proximity to the signal wire, power and ground wires connecting Chip A and Chip B. This isn't practical on a wireless breadboard (or a 2-layer PCB), but you can achieve some of the same benefit by forming the Power & Ground Distribution network into a coarse grid (a fine grid is even better). Remember: the goal is that, for any signal from one chip to another, you want the return current to be able to follow much the same path, in close proximity, back to the first chip.

In the first diagram below I've highlighted your Power & Ground Distribution network, and we can see that, as a grid, it has many serious gaps. If this were the roadmap of a city we'd say it has far too many cul de sacs, making driving a nightmare. The second diagram shows some possible connections you could add to provide relief to the frustrated drivers!

And, here's another diagram suggesting a further improvement. Since you have several bundles of conductors in midair, vertically separated from the grid, you would do well to add at least a ground wire in close proximity to each of those bundles. Because the goal is to conduct current, both end points (not just one) need to attach to the local ground. (And if there are three or more end points, all should ideally be grounded.) Hope this helps. I think we could also improve the way your bypass capacitors are arranged, but that's a topic for another post.

The WDC '816 is always challenge, due to the very fast transitions on its outputs. And with a breadboard project of this size you may only find it possible to reduce the number of glitches, rather than eliminating them entirely.

BTW you may also want to see my recent post here, also on the subject of Power & Ground Distribution grids.

-- Jeff

Last edited by Dr Jefyll on Tue Feb 22, 2022 7:09 pm, edited 1 time in total.

In 1988 my 65C02 got six new registers and 44 new full-speed instructions!

https://laughtonelectronics.com/Arcana/ ... mmary.html

https://laughtonelectronics.com/Arcana/ ... mmary.html

Re: 65C816 Computer YouTube Series

Dr Jefyll wrote:

It's best to avoid thinking of the Power & Ground Distribution network as something for connecting the chips to the power supply. Where high frequencies are concerned, its real job is to connect the chips to one another.

Bill

- akohlbecker

- Posts: 282

- Joined: 24 Jul 2021

- Contact:

Re: 65C816 Computer YouTube Series

Thank you both for the great information! And even with pictures!

I've been avoiding making those ground connections for fear of creating ground loops. I guess I need to reconsider that

I've been avoiding making those ground connections for fear of creating ground loops. I guess I need to reconsider that

Re: 65C816 Computer YouTube Series

akohlbecker wrote:

... I think the length of my data bus and address bus wires is causing reflections ...

That prompted me to make a speed test build as compact as possible.

I could only operate the build with longer buses at 2 MHz but the more compact one at 10 MHz.

btw: great video series. I've learned a lot and hope to incorporate some of your ideas into my 65816 build.

Re: 65C816 Computer YouTube Series

Just a little hint, tmr4. On this forum you're allowed to attach images with your posts. You'll find this more convenient than hosting images off-site, and furthermore the images will remain available long-term for future readers of the forum. Cheers,

Jeff

Jeff

In 1988 my 65C02 got six new registers and 44 new full-speed instructions!

https://laughtonelectronics.com/Arcana/ ... mmary.html

https://laughtonelectronics.com/Arcana/ ... mmary.html

- akohlbecker

- Posts: 282

- Joined: 24 Jul 2021

- Contact:

Re: 65C816 Computer YouTube Series

tmr4 wrote:

btw: great video series. I've learned a lot and hope to incorporate some of your ideas into my 65816 build.

And thanks for sharing your build. The difference in speed is massive indeed.

- akohlbecker

- Posts: 282

- Joined: 24 Jul 2021

- Contact:

Re: 65C816 Computer YouTube Series

Also, I didn't post the regular video update yet! Episode 18 is out!

In that episode, I discuss the purpose of the VDA and VPA pins. I then add them to my debug LEDs and to my Arduino monitor.

I also start re-working my read-write pulses, to incorporate VDA/VPA and also RDY and BE. This leads to some interesting timing problems, which I'm hoping to solve next time with a new clock phase

In that episode, I discuss the purpose of the VDA and VPA pins. I then add them to my debug LEDs and to my Arduino monitor.

I also start re-working my read-write pulses, to incorporate VDA/VPA and also RDY and BE. This leads to some interesting timing problems, which I'm hoping to solve next time with a new clock phase

Re: 65C816 Computer YouTube Series

Dr Jefyll wrote:

Just a little hint, tmr4. On this forum you're allowed to attach images with your posts...

- Sheep64

- In Memoriam

- Posts: 311

- Joined: 11 Aug 2020

- Location: A magnetic field

Re: 65C816 Computer YouTube Series

As noted by Dr Jefyll, you've got fans and followers. However, they are copying some of your more exploratory steps without success.

I'm glad that you dumped the 74HC4078. I bought one to settle an argument with the argumentative BigDumbDinosaur. However, when I had it in my hoof (see username), I realized that it wasn't necessary. Instead, I devised a much faster scheme which treats all banks symmetrically. (Diagrams.)

Low frequency audio and a ground loop with large area should be avoided. High frequency digital and a ground loop with small area is highly desirable.

Tangentially related: Metal film resistors are usually best for low frequency audio and carbon resistors are usually best for high frequency digital. This is due to high inductance of metal film resistors and hiss from carbon resistors.

General principle: Electronics advice may not apply to your domain.

I'm glad that you dumped the 74HC4078. I bought one to settle an argument with the argumentative BigDumbDinosaur. However, when I had it in my hoof (see username), I realized that it wasn't necessary. Instead, I devised a much faster scheme which treats all banks symmetrically. (Diagrams.)

akohlbecker on Tue 22 Feb 2022 wrote:

fear of creating ground loops.

Tangentially related: Metal film resistors are usually best for low frequency audio and carbon resistors are usually best for high frequency digital. This is due to high inductance of metal film resistors and hiss from carbon resistors.

General principle: Electronics advice may not apply to your domain.

- GARTHWILSON

- Forum Moderator

- Posts: 8773

- Joined: 30 Aug 2002

- Location: Southern California

- Contact:

Re: 65C816 Computer YouTube Series

Sheep64 wrote:

Tangentially related: Metal film resistors are usually best for low frequency audio and carbon resistors are usually best for high frequency digital. This is due to high inductance of metal film resistors and hiss from carbon resistors.

http://WilsonMinesCo.com/ lots of 6502 resources

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

- BigDumbDinosaur

- Posts: 9425

- Joined: 28 May 2009

- Location: Midwestern USA (JB Pritzker’s dystopia)

- Contact:

Re: 65C816 Computer YouTube Series

Sheep64 wrote:

Tangentially related: Metal film resistors are usually best for low frequency audio and carbon resistors are usually best for high frequency digital.

Technically, that is true, but some pink noise (aka hiss) is part and parcel of the vacuum tube audio amplifier era, no matter the resistor type (carbon comp in those days). Most of the hiss was thermionic noise being emitted by the tubes, especially in the early stages of amplification. Add to that the hiss generated by analog magnetic tape, along with a smattering of power supply ripple and traces of common mode hum, and you have what passed for “high fidelity” back when Eisenhower was the US president. My old Ampeg B15N bass amp has similar characteristics, just louder than what I had when I was in eighth grade, when a 20 watt amp was a real powerhouse.

As Garth noted, the tiny bit of inductance introduced by the spiral trim of a film resistor is usually of little-to-no consequence—lead lengths and general construction techniques will have more influence in most cases.

x86? We ain't got no x86. We don't NEED no stinking x86!