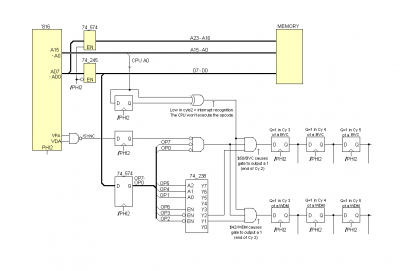

Following on from this post I've tried detecting interrupts BEFORE any of the stack pushes occur; and using Dr Jefyll's schematic below

Attachment:

wavery00.png [ 14.9 KiB | Viewed 586 times ]

wavery00.png [ 14.9 KiB | Viewed 586 times ]

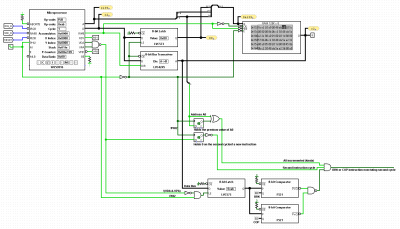

I've simulated up the following for detecting software interrupts:

Attachment:

SoftwareInterrupt.png [ 59.6 KiB | Viewed 586 times ]

SoftwareInterrupt.png [ 59.6 KiB | Viewed 586 times ]

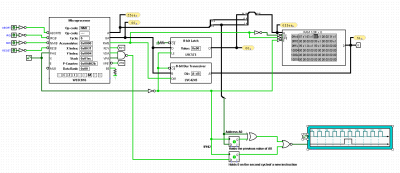

and hardware interrupts:

Attachment:

HardwareInterrupt.png [ 44.33 KiB | Viewed 586 times ]

HardwareInterrupt.png [ 44.33 KiB | Viewed 586 times ]

And both cases seem to work quite nicely. Excellent!

I have made a change to the latching logic to only latch the opcode when PHI2 is high and VDA and VPA are also both high. It might be overkill but if I ever have a need to know the opcode I'll have it sitting in that latch.

I've changed the '574 to a '573 because the '574 is a chonky boi. The SO20 takes up a LOT of space whereas the '573 is available as a TSSOP20.

I'm using a pair of comparators for a couple of reasons firstly I don't want to have to muck around with a bunch of NAND gates and inverters each of which cost the same as the comparator and secondly it makes testing for other opcodes much easier. I'll probably also swap the 'F521 for an 'HC688 (because again, the 'F521 is another chonky boi) but this is all still simulation land.

I've separated the circuits into hardware and software to make it easier for me to understand but ultimately to add hardware interrupt detection into the software circuit only needs a single NOR gate.

And that's a big thank you to everyone on this forum for the help. It's very much appreciated

(and after all of this I've realised I may have a problem switch back to user mode on the RTI leg ... but that's a problem for another time)

(and after all of this I've realised I may have a problem switch back to user mode on the RTI leg ... but that's a problem for another time)