ACIA Works for 65c02, not for 65c816 with same settings?

ACIA Works for 65c02, not for 65c816 with same settings?

I've been tinkering and testing with my ACIAs (65c51 and LIV2's RTL equivalent) all week, when I had time. The issue is that, when I connect my 65c02 with a 4mhz or 6mhz clock, along with a 1.8432hmz connected to the ACIA, RTL or physical, it works just fine, no problem. However, when I swap out the 65c02 for a 65c816, I run into trouble.

I tested the setup with the VIO (effectively a logic analyzer I can single-step) on my Xilinx CMOD A7, and I've confirmed that the 65c816 itself, along with its ram and rom, work just fine. But the output from the ACIA is garbled. Some of it is correct, some isn't. The output looks fine, then it staggers and skips or prints garbage, then returns to printing what it is supposed to. I've tried with both an RTL ACIA and the real, physical ACIA (at 5V after a logic level shifter), and the result is the same.

Now, I know on the timing on the RAM is effected by the duplexed data lines. Is the ACIA?

I'm at my wit's end here.

Jonathan

PS If you have a CMOD A7 35T and a 65c816, my code is here: https://github.com/jmstein7/65c02-FPGA- ... bench.srcs

I tested the setup with the VIO (effectively a logic analyzer I can single-step) on my Xilinx CMOD A7, and I've confirmed that the 65c816 itself, along with its ram and rom, work just fine. But the output from the ACIA is garbled. Some of it is correct, some isn't. The output looks fine, then it staggers and skips or prints garbage, then returns to printing what it is supposed to. I've tried with both an RTL ACIA and the real, physical ACIA (at 5V after a logic level shifter), and the result is the same.

Now, I know on the timing on the RAM is effected by the duplexed data lines. Is the ACIA?

I'm at my wit's end here.

Jonathan

PS If you have a CMOD A7 35T and a 65c816, my code is here: https://github.com/jmstein7/65c02-FPGA- ... bench.srcs

Re: ACIA Works for 65c02, not for 65c816 with same settings?

I would start by upgrading your use of supply bypass capacitors, reconsidering how many are present and the manner in which they're connected. Due to its multiplexed data bus the '816 can generate a lot more supply noise than the '02 or 'C02, and supply noise is a plausible cause of intermittent failures such as the ones you describe.

For anyone who's interested, this thread details some extremely

unlikely-seeming symptoms which were eventually explained by inadequate '816 supply bypassing.

unlikely-seeming symptoms which were eventually explained by inadequate '816 supply bypassing.

-- Jeff

For anyone who's interested, this thread details some extremely

-- Jeff

In 1988 my 65C02 got six new registers and 44 new full-speed instructions!

https://laughtonelectronics.com/Arcana/ ... mmary.html

https://laughtonelectronics.com/Arcana/ ... mmary.html

Re: ACIA Works for 65c02, not for 65c816 with same settings?

Dr Jefyll wrote:

I would start by upgrading your use of supply bypass capacitors, reconsidering how many are present and the manner in which they're connected. Due to its multiplexed data bus the '816 can generate a lot more supply noise than the '02 or 'C02, and supply noise is a likely cause of intermittent failures such as the ones you describe.

For anyone who's interested, this thread details some extremely

unlikely-seeming symptoms which were eventually explained by inadequate '816 supply bypassing.

unlikely-seeming symptoms which were eventually explained by inadequate '816 supply bypassing.

-- Jeff

For anyone who's interested, this thread details some extremely

-- Jeff

Re: ACIA Works for 65c02, not for 65c816 with same settings?

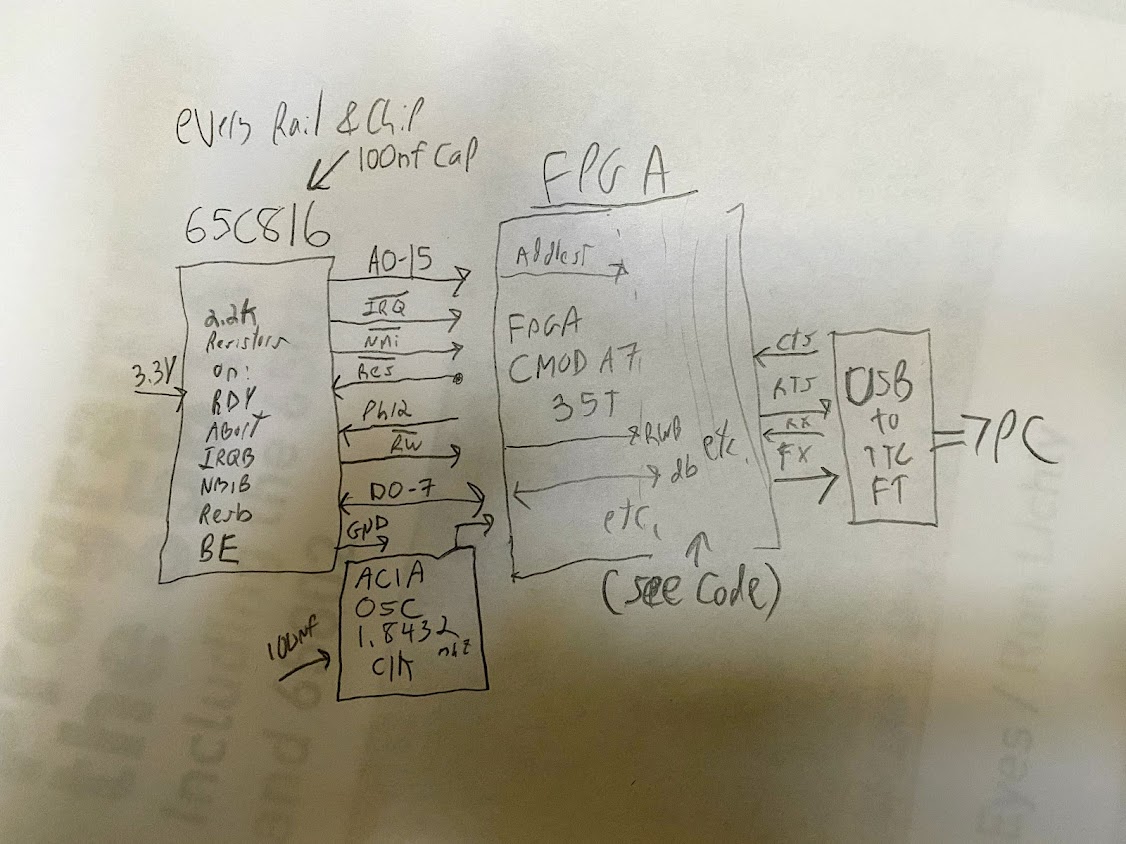

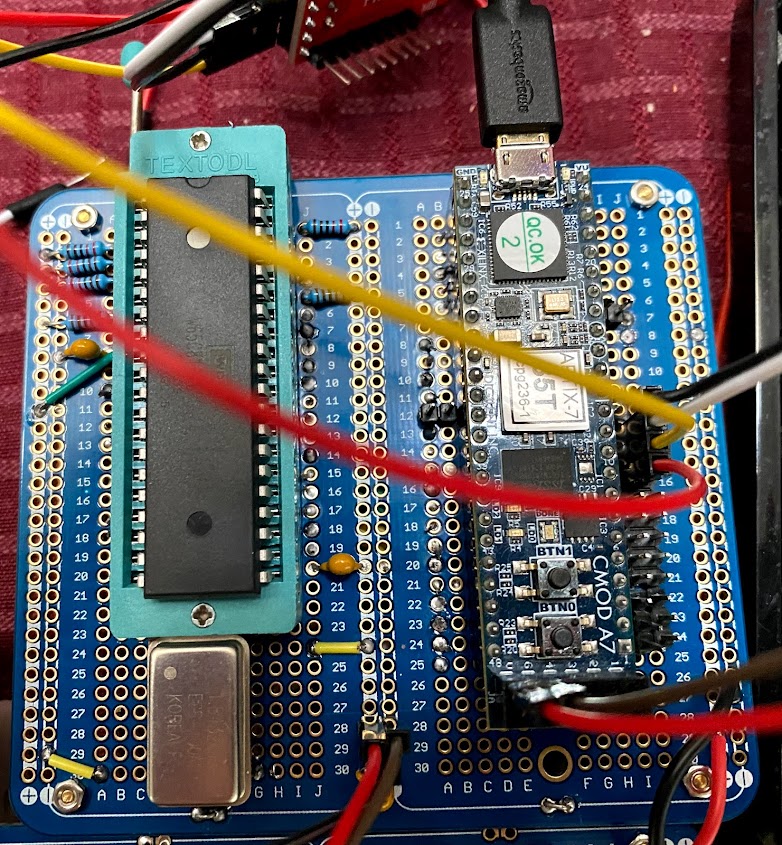

You've started a new thread without linking to what went before. Is this the project you're talking about? And are those photos still up to date?

Also, nice if you can post a schematic, please -- here, I mean, rather than off-site. Cheers,

Jeff

Also, nice if you can post a schematic, please -- here, I mean, rather than off-site. Cheers,

Jeff

In 1988 my 65C02 got six new registers and 44 new full-speed instructions!

https://laughtonelectronics.com/Arcana/ ... mmary.html

https://laughtonelectronics.com/Arcana/ ... mmary.html

Re: ACIA Works for 65c02, not for 65c816 with same settings?

Dr Jefyll wrote:

You've started a new thread without linking to what went before. Is this the project you're talking about? And are those photos still up to date?

Also, nice if you can post a schematic, please -- here, I mean, rather than off-site. Cheers,

Jeff

Also, nice if you can post a schematic, please -- here, I mean, rather than off-site. Cheers,

Jeff

Re: ACIA Works for 65c02, not for 65c816 with same settings?

Dr Jefyll wrote:

Is this the project you're talking about? And are those photos still up to date?

So, do you still want some help with "my ACIAs (65c51 and LIV2's RTL equivalent)", then? Whatever that is.

It's confusing trying to guess what you're up to, so please help us out by sharing the details! So far all I know for sure is, you have some sort of project and you swapped out an '02 for an '816. Based on that alone I've made an educated guess. But if you want help upgrading the bypass caps, or any other kind of help, please please tell us what you're doing! Photos & a schematic, too, please.

-- Jeff

Last edited by Dr Jefyll on Sun Sep 19, 2021 6:01 pm, edited 1 time in total.

In 1988 my 65C02 got six new registers and 44 new full-speed instructions!

https://laughtonelectronics.com/Arcana/ ... mmary.html

https://laughtonelectronics.com/Arcana/ ... mmary.html

Re: ACIA Works for 65c02, not for 65c816 with same settings?

Dr Jefyll wrote:

Arghh! So, do you still want some help with "my ACIAs (65c51 and LIV2's RTL equivalent)", then? Whatever that is.

It's confusing trying to guess what you're up to, so please help us out by sharing the details! So far all I know for sure is, you have some sort of project and you swapped out an '02 for an '816.

I've made an educated guess based on that alone. But if you want help upgrading the bypass caps, or any other kind of help, please please tell us what you're doing! Photos & a schematic, too, please.

-- Jeff

It's confusing trying to guess what you're up to, so please help us out by sharing the details! So far all I know for sure is, you have some sort of project and you swapped out an '02 for an '816.

I've made an educated guess based on that alone. But if you want help upgrading the bypass caps, or any other kind of help, please please tell us what you're doing! Photos & a schematic, too, please.

-- Jeff

I'm going to just draw it out and take a pic. What kind of pic files can we attach to posts? JPG? I want to keep it on-site.

Re: ACIA Works for 65c02, not for 65c816 with same settings?

Dr Jefyll wrote:

Dr Jefyll wrote:

Is this the project you're talking about? And are those photos still up to date?

So, do you still want some help with "my ACIAs (65c51 and LIV2's RTL equivalent)", then? Whatever that is.

It's confusing trying to guess what you're up to, so please help us out by sharing the details! So far all I know for sure is, you have some sort of project and you swapped out an '02 for an '816. Based on that alone I've made an educated guess. But if you want help upgrading the bypass caps, or any other kind of help, please please tell us what you're doing! Photos & a schematic, too, please.

-- Jeff

Connections: https://photos.google.com/u/2/share/AF1 ... RMZmxFOERn

Picture: https://photos.google.com/u/2/share/AF1 ... RMZmxFOERn

The pics show the caps - except that the oscillator has it on the bottom.

Jonathan

And, code: https://github.com/jmstein7/65c02-FPGA- ... bench.srcs

- BigDumbDinosaur

- Posts: 9428

- Joined: 28 May 2009

- Location: Midwestern USA (JB Pritzker’s dystopia)

- Contact:

Re: ACIA Works for 65c02, not for 65c816 with same settings?

Jmstein7 wrote:

PS If you have a CMOD A7 35T and a 65c816, my code is here: https://github.com/jmstein7/65c02-FPGA- ... bench.srcs

It would be quite helpful if you would attach things such as code and schematics to your posts instead of making readers go off-site to see such material. I'd like to help but I don't do Github or Google.

x86? We ain't got no x86. We don't NEED no stinking x86!

- BigDumbDinosaur

- Posts: 9428

- Joined: 28 May 2009

- Location: Midwestern USA (JB Pritzker’s dystopia)

- Contact:

Re: ACIA Works for 65c02, not for 65c816 with same settings?

Dr Jefyll wrote:

I would start by upgrading your use of supply bypass capacitors...

Also, a FULL schematic would be a BIG help. You can't expect anyone to troubleshoot a circuit if they haven't a clue about how it's hooked up.

x86? We ain't got no x86. We don't NEED no stinking x86!

Re: ACIA Works for 65c02, not for 65c816 with same settings?

How's this? I'm pretty new to this, still, and my fine motor skills stink

Code: Select all

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 09/17/2021 03:16:14 PM

// Design Name:

// Module Name: top

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module top(

input logic clk,

input logic acia_clk,

input logic e_bit,

input logic vpa,

input logic vda,

input logic reset,

input logic rwb,

input logic [15:0] ab,

inout logic [7:0] db,

output logic phi2,

output logic nmib,

output logic irqb,

output logic resb,

//mode_2

//inout logic [7:0] data,

//output logic acia_e,

//sram IO

inout wire [7:0] dio_a,

output reg [15:0] ad,

output reg oe_n,

output reg we_n,

output reg ce_a_n,

//ACIA IO

output wire rts,

output wire tx,

input wire rx,

input wire cts

);

logic [7:0] bank;

logic bank_enable;

logic db_enable;

logic rom_enable;

logic ram_enable;

logic [7:0] data_w;

logic [7:0] data_r;

logic [7:0] read_data;

logic [15:0] address;

logic [7:0] rom_out;

logic mrd_n, mrw_n;

logic [7:0] ram_in;

logic [7:0] ram_out;

logic [7:0] acia_in;

logic [7:0] acia_out;

logic acia_irq;

//fixed

assign bank_enable = (~phi2) ? 1'b1 : 1'b0;

assign db_enable = (~phi2) ? 1'b0 : 1'b1;

assign mrw_enable = (phi2) ? 1'b1 : 1'b0;

assign data_rw = (rwb) ? 1'b1 : 1'b0;

assign address = ab;

assign rom_enable = (address >= 16'hC000) ? 1'b1 : 1'b0;

assign ram_enable = (address < 16'h8000) ? 1'b1 : 1'b0;

assign acia_enable = (address >= 16'h8000 && address < 16'h8010) ? 1'b1 : 1'b0;

//mode_2

//assign acia_e = ~acia_enable;

//mrd and mrw signals

assign mwr_n = (mrw_enable && ~rwb) ? 1'b0 : 1'b1;

assign mrd_n = (mrw_enable && rwb) ? 1'b0 : 1'b1;

//bank address latch

always_latch begin

if (bank_enable) begin

bank = db;

end

//No else clause so a_latch's value

//is not always defined, so it holds its value

end

/* base model

assign db = (db_enable) ? (rwb ? read_data : 'bz): 'bZ,

data_w = (db_enable) ? (~rwb ? db : 'bZ) : 'bZ,

resb = ~reset,

irqb = 1,

nmib = 1;

*/

assign db = (db_enable) ? (rwb ? (rom_enable ? rom_out : (ram_enable ? ram_out : (acia_enable ? acia_out : 'bZ))) : 'bZ) : 'bZ,

data_w = (db_enable) ? (~rwb ? db : 'bZ) : 'bZ,

resb = ~reset,

irqb = 1,

nmib = 1;

assign ram_in = (ram_enable && ~rwb) ? data_w : 'bZ;

assign acia_in = (acia_enable && ~rwb) ? data_w : 'bZ;

/*

//mode_2

assign data = (data_rw) ? 'bZ : acia_in;

assign acia_out = (data_rw) ? data : 'bZ;

*/

ACIA acia_a(

.RESET(resb),

.PHI2(phi2),

.CS(acia_e),

.RWN(rwb),

.RS(address),

.DATAIN(acia_in),

.DATAOUT(acia_out),

.XTLI(acia_clk),

.RTSB(rts),

.CTSB(cts),

.DTRB(),

.RXD(rx),

.TXD(tx),

.IRQn(1'b1)

);

sram_ctrl5 ram_0(

.clk(phi2),

.rw(rwb),

.wr_n(mwr_n),

.rd_n(mrd_n),

.ram_e(ram_enable),

.address_input(address),

.data_f2s(ram_in),

.data_s2f(ram_out),

.address_to_sram_output(ad),

.we_to_sram_output(we_n),

.oe_to_sram_output(oe_n),

.ce_to_sram_output(ce_a_n),

.data_from_to_sram_input_output(dio_a)

);

dist_mem_gen_0 rom_0(

.a(address),

.spo(rom_out)

);

//Clock Divider

/*

clk_wiz_0 clock_a(

// Clock out ports

.phi2(phi2),

// Status and control signals

.reset(reset),

.locked(),

// Clock in ports

.clk(clk)

);

*/

//fixed

/*

vio_0 debug_core(

.clk(clk),

.probe_in0(ab),

.probe_in1(db),

.probe_in2(rwb),

.probe_in3(acia_e),

.probe_in4(vda),

.probe_in5(vpa),

.probe_in6(reset),

.probe_in7(bank),

.probe_in8(data_w),

.probe_in9(data),

.probe_out0(phi2)

);

*/

endmodule

Re: ACIA Works for 65c02, not for 65c816 with same settings?

I'm willing to believe you're trying, but you need to try harder. For example your schematic shows an ACIA but the photo shows none, or even a possible site for one. What's the explanation?? And can we see the underside of that board, please?

Going back to general principles, I hope you know the 816's pinout doesn't entirely match that of the 'C02. So, your remark in the lead post about swapping out the 65c02 for a 65c816 leaves me wondering. Are there some jumpers you adjust when you make the swap?

Regarding the HDL code you posted: does your FPGA float the data bus to high impedance when Phi2 is low? The '816 requires this, but the '02 does not.

-- Jeff

Going back to general principles, I hope you know the 816's pinout doesn't entirely match that of the 'C02. So, your remark in the lead post about swapping out the 65c02 for a 65c816 leaves me wondering. Are there some jumpers you adjust when you make the swap?

Regarding the HDL code you posted: does your FPGA float the data bus to high impedance when Phi2 is low? The '816 requires this, but the '02 does not.

-- Jeff

In 1988 my 65C02 got six new registers and 44 new full-speed instructions!

https://laughtonelectronics.com/Arcana/ ... mmary.html

https://laughtonelectronics.com/Arcana/ ... mmary.html

Re: ACIA Works for 65c02, not for 65c816 with same settings?

Dr Jefyll wrote:

I'm willing to believe you're trying, but you need to try harder. For example your schematic shows an ACIA but the photo shows none, or even a possible site for one. What's the explanation?? And can we see the underside of that board, please?

Going back to general principles, I hope you know the 816's pinout doesn't entirely match that of the 'C02. So, your remark in the lead post about swapping out the 65c02 for a 65c816 leaves me wondering. Are there some jumpers you adjust when you make the swap?

Regarding the HDL code you posted: does your FPGA put the data bus to high impedance when Phi2 is low? The '816 requires this, but the '02 does not.

-- Jeff

Going back to general principles, I hope you know the 816's pinout doesn't entirely match that of the 'C02. So, your remark in the lead post about swapping out the 65c02 for a 65c816 leaves me wondering. Are there some jumpers you adjust when you make the swap?

Regarding the HDL code you posted: does your FPGA put the data bus to high impedance when Phi2 is low? The '816 requires this, but the '02 does not.

-- Jeff

Re: ACIA Works for 65c02, not for 65c816 with same settings?

The main "glitch" right now is that the ACIA seems to clip the first letter or two of each line of text. It also isn't doing the LFs or CRs in the correct places (e.g., at the end of said lines). Otherwise, the text is clear. Of course, RX doesn't work at all, and I can't type anything in. Finally, after printing the text, it hangs.

Re: ACIA Works for 65c02, not for 65c816 with same settings?

In the lead post you said, "I've been tinkering and testing with my ACIAs (65c51 and LIV2's RTL equivalent)," which sounds as if you meant a real, physical 65c51 as well as the soft core.

Edit: I see you've posted again, but my advice remains the same. Please consider what I said about the '816 needing its data bus NOT to be driven during Phi2 low, as ignoring this detail would cause supply noise which might be the cause of your trouble. I have no further advice to offer at this time -- gonna shut down the screens and get out into the sunshine.

-- Jeff

Edit: I see you've posted again, but my advice remains the same. Please consider what I said about the '816 needing its data bus NOT to be driven during Phi2 low, as ignoring this detail would cause supply noise which might be the cause of your trouble. I have no further advice to offer at this time -- gonna shut down the screens and get out into the sunshine.

-- Jeff

In 1988 my 65C02 got six new registers and 44 new full-speed instructions!

https://laughtonelectronics.com/Arcana/ ... mmary.html

https://laughtonelectronics.com/Arcana/ ... mmary.html