Hi Risc,

atf22v10c.pdf

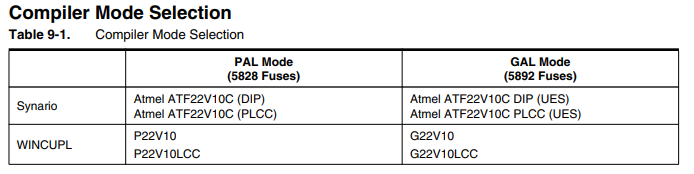

You tell WinCUPL which device you are using in the header of your design file. It's all explained in the help files that are part of WinCUPL. The correct device is

g22v10.

is a useful starting point but I've found that the Atmel datasheet kinda assumes you know what a 22V10 does. I've found the Lattice datasheet to be a little more helpful

http://web.mit.edu/6.115/www/document/gal22v10.pdf.

The macro cell itself is really just a D type flip flop plus a couple of multiplexers. The multiplexers allow the output to be either a combinational or sequential function. Lattice datasheet pg. 3 makes this clear and pg. 4 takes you through all the possible configurations. Note that these are selected during programming and cannot be changed once the chip is in use. The Atmel chip functions the same, just not as well documented.

Your original question was along the lines of "how can I tell if my function will fit?". Unfortunately it really depends on the complexity of your application.

My apologies if you already understand this bit. Looking at the Lattice pg. 5 you'll see the chip laid out schematically. The vertical lines are numbered 0 to 43. They are connected to either the chip inputs or to a macrocell. If the macrocell is configured to operate sequentially, i.e. flip flop, then the value is taken from the flip flops /Q output. If the macrocell is combinational then the value comes from the output pin itself, it basically gives you another input pin.

The vertical lines form complementary pairs, that is a signal plus its inverse. For example, vertical 0 is hardwired to pin 1, vertical 1 is pin 1 inverted (not pin 1). Verticals 2&3 are connected to feedback from macrocell 1, with vertical 2 being the opposite polarity to vertical 3. All up there are 22 input signals available in their positive and negative logic levels.

The horizontal lines (rows) labelled with four digit numbers form the AND/OR array. This is also known as the sum of products array. Each of these horizontal lines feeds into an AND gate. Each AND gate has 44 inputs, the verticals mentioned previously. The output of each AND gate is fed into a large OR gate. The OR gates vary in size between 8 and 16 inputs. Macrocells 1 & 10 (top & bottom) have the smallest OR gates (8 inputs). Macrocells 5&6 (middle) have the biggest, 16 inputs each. This difference can be important and is expanded later.

The way GAL's work is that there is a programmable fuse at each and every intersection between the vertical and horizontal lines.

Each fuse has a number and they are organised by row and column. The fuse number is given by the row plus the column number. For example, row 44 controls the output enable for pin 23. If I wanted to control this using pin 2 (active high) then I need to connect row 44 to column 4. This means fuse 48 needs to be programmed/connected. If I wanted to use pin 2 (active low) then I need to connect row 44 and column 5, i.e. fuse 49. If this was the only input used then the other 43 columns would be left disconnected. Whilst this sounds complicated you don't normally have to deal with the fuse map unless there is a problem.

The WinCUPL software takes your logic equations and works out which fuses it needs to connect, i.e. it does all the row/column calculations for you. You can always get to the data, WinCUPL puts this into one of its reports, I think it's the fuse map but don't have it handy right now.

Will your stuff fit? Try it and see. If you get warned about a function being too complex for a single macrocell you can either 1) move it to a macrocell with a larger OR gate or 2) combine the output of one macrocell with the inputs from another i.e. use 2 macrocells to give you more space in the AND/OR array.

I hope you find this stuff useful.