I've been giving some thought to the physical construction of my computer. I'm thinking that there'll be a longish bus board that has the five buses (WB, RB, ADL, ADH, and DB) running in parallel, along with tracks for power and clocks. If power is +5v, GND, and clocks are CLK, PHI1, PHI2, then the board will essentially be 45 tracks, and for prototyping I could use some stripboard (like this https://www.ebay.co.uk/itm/Stripboard-1 ... 3074484745). Each card sits vertically, having right-angled Dupont headers for attaching to the bus board.

I've also been designing the register card, abandoning the dual-register-per-card idea in favour of a much simpler single 8-bit register. I also decided to simplify things somewhat and go with using a pair of 74HC161 chips for each register, since they will work nicely as both static registers and counters. The idea here is that I can use one card for each register, with the exception of the status register, hence the generic design.

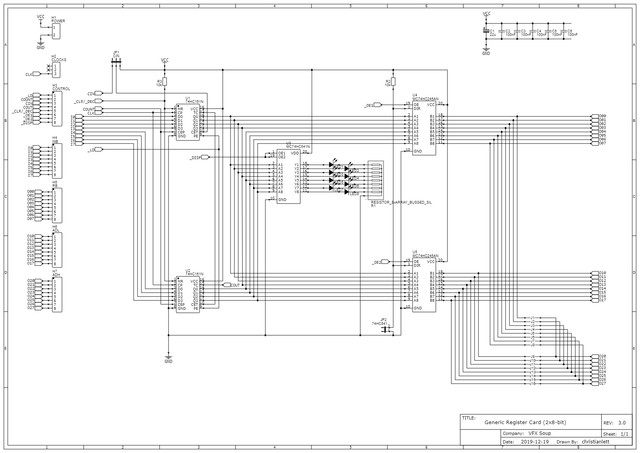

Here's the schematic:

The '161s take their input from the W bus directly, and output to the display LEDs via a 74HC541 buffer. The reason for this is so I can turn the LEDs on and off globally using the _DISP control wire if running in fast mode, as well as ensuring the signal integrity due to power draw from the LEDs.

Each register can but output to two of the three output buses. The outputs are buffered using a pair of 74HC245s (or 541s if preferred as they have almost identical pinouts except for pin 1. A pullup resistor sets pin 1 on the '245 to direction A->B, and using the jumper pulls the pin to ground to turn on one of the OE controls if using the '541). I happen to have quite a few '245 chips, which is why I'm using them but it was easy enough to add in the flexibility to use the unidirectional buffer if needed.

A series of jumpers sets the ADH output to use either one of the two output buffers.

I'll be prototyping it using breadboards soon to make sure it works.

As for the Stack Register, I've been considering using the 74LS169 as suggested by Deiter. Conceptually it can replace the '161s directly with no modifications to the circuitry, because the pinout is identical. The _CLR/_DEC control wire will either be floating for the majority of cards (the _CLR control is reserved for another time...), so pin 1 (_MR) on the '161 is pulled high by R3, or set appropriately for the Stack Register. Aside from the LS169's eye-wateringly high power consumption (100mW!) and cost (£1.50 per chip!) the obvious concern is mixing TTL with CMOS. Am I correct in thinking that replacing the LED and output buffers with HCT versions will allow this to work? I'm using only 5V for power, input voltage will be high enough to drive the TTL. The HCT chips can take TTL level inputs and output VCC, so the buses will be driven at the same voltages as from the all-CMOS cards. Is that right?

[EDIT]I've just noticed that the LS169 uses active low count enable pins, whereas the HC161's are active high - same for the RCO. So the circuit will require a small rework but nothing too complex[/EDIT]

As usual all comments and suggestions gratefully received.

Thanks, Christian