Since availability of 74F85 and 74AC85 doesn't look good, this posting won't be useful for _this_ project,

but maybe somebody could turn the concept into something useful later in the future (you never know).

Be warned, that it's all untested... and just theory.

Might contain some errors, don't expect things to work at first try.

;---

While flipping through the pages of the 1985 Fairchild 74F data book at Bitsavers,

the picture on page 4-29 (page 74 of the PDF) about cascading 74F85 magnitude comparators had caught my attention:

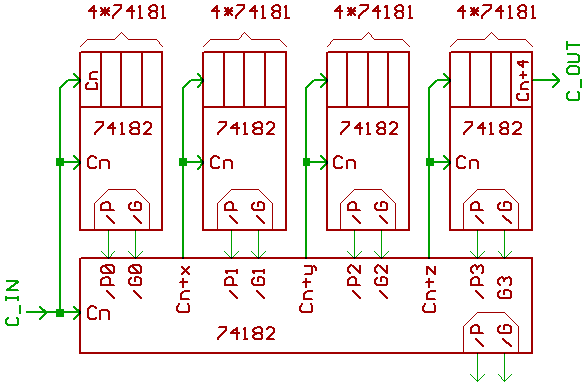

It somehow reminded me to cascading 74182 carry lookahead chips:

;...

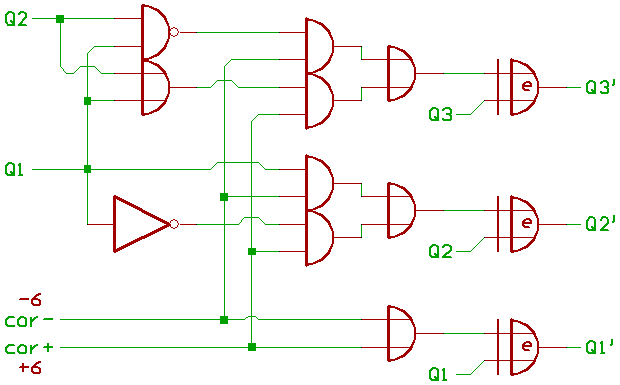

7485 is optimized for speed, so it isn't obvious from the gate level schematic in the 7485 datasheet,

but when drawing a (slower) Bit_sliced version of a magnitude comparator, I'm getting something like this for a single Bit:

The light_blue marked part is the logic which detects A>B, and when re_drawing that part a few times,

it appears to be just subtractor circuitry calculating A-B by inverting B (similar to how SBC works in the 6502 ALU).

;...

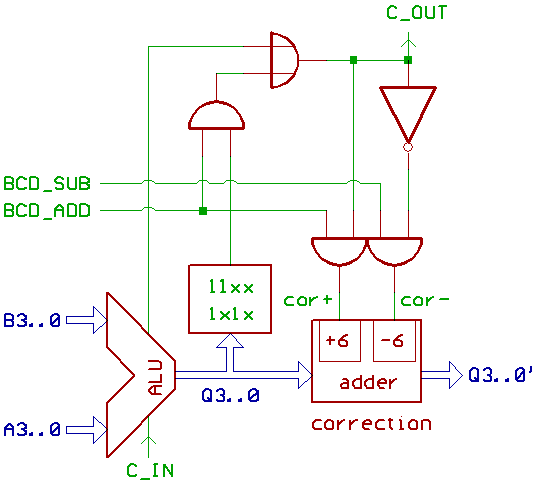

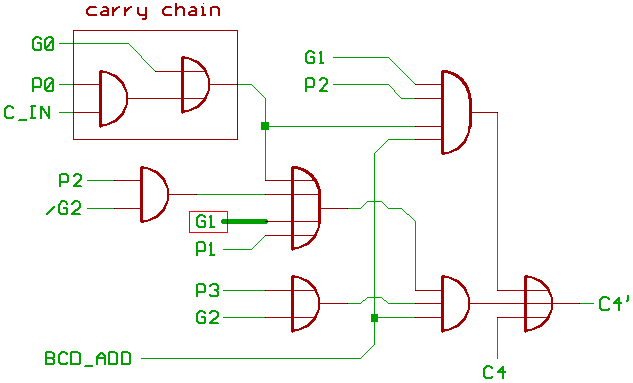

So when we have a 4 Bit adder, and we want to build a 4 Bit carry lookahead circuitry for the adder carry output,

in theory we could just take a 7485 magnitude comparator and invert the comparator B input:

;....

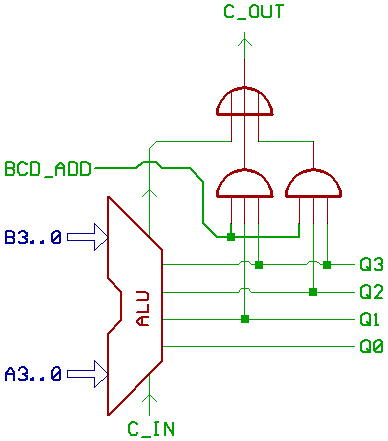

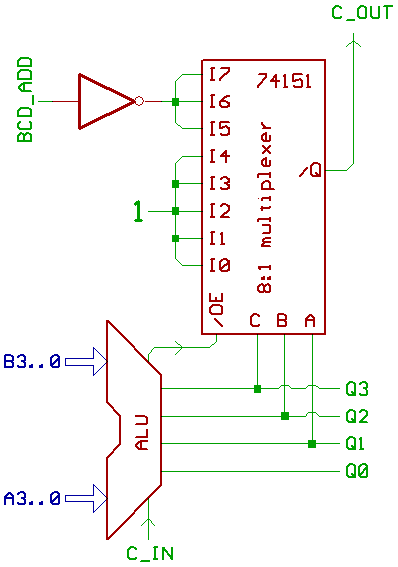

Now for a (hypothetical) 4 Bit ALU, with a 7485 based carry chain:

The boxes labeled "LU" are logic units based on 74153 4:1 multiplexers.