Quote:

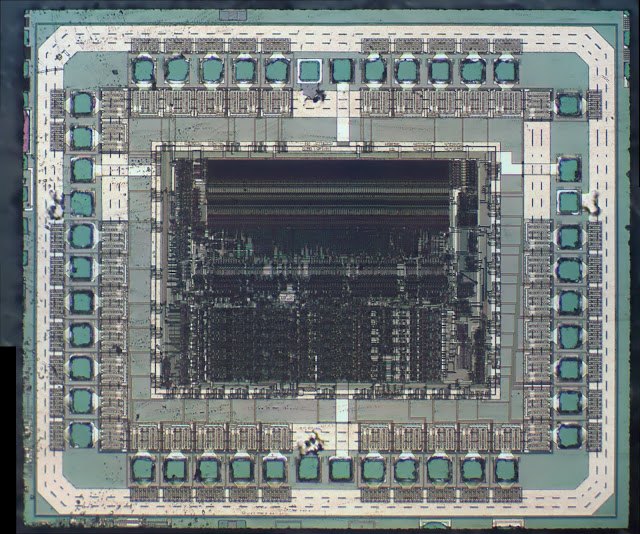

This particular version was plucked off of an embedded industrial controller... a place where this processor still finds design wins. The die has patent numbers which were very helpful in sorting down the details of this design.

Blog:

I think some of the commentary on the chip is not quite right. I would say the floorplan is very like the NMOS 6502 - the area below the decode array will be the so-called random logic, and the more organised area in the bottom half of the core will be the datapath - that's where you'll find the registers, the ALU, and the busses. Note that the decode array doesn't have fuses - it is mask-programmed - but the variable features are indeed the programming of the array.

Lots of white space in the chip, as noted - looks pad-limited, which is not great for price, as the core is such a small part of the silicon.