Code: Select all

module LineGen( input clk108,

input countflag, //flag, plot inside borders

input vblank,

input vsync,

output reg [15:0] X, //H component of pixel to BRAM

output reg [15:0] Y //V component of pixel to BRAM

);

reg [15:0] x0;

reg [15:0] y0;

reg [15:0] x1;

reg [15:0] y1;

reg [15:0] dx;

reg [15:0] dy;

reg [15:0] num;

reg [15:0] e2;

reg [0:0] sx;

reg [2:0] state;

parameter init_state = 0, prep_state = 1, Hplot_state = 2, Vplot_state = 3;

always @(posedge clk108)

if ( vblank & vsync )

state <= init_state;

else

case (state)

init_state :

state <= prep_state;

prep_state :

if ( countflag )

if ( dx > dy )

state <= Hplot_state;

else

state <= Vplot_state;

Hplot_state :

if ( !countflag )

state <= init_state;

Vplot_state :

if ( !countflag )

state <= init_state;

endcase

always @(posedge clk108) begin

case (state)

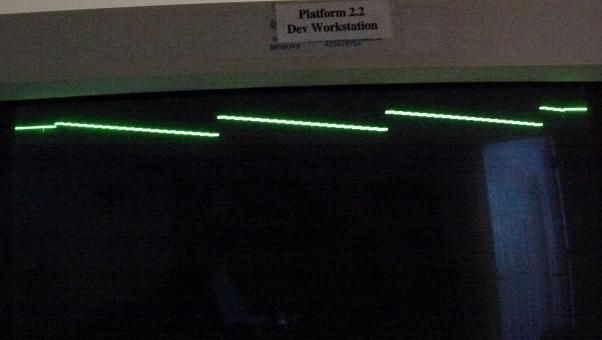

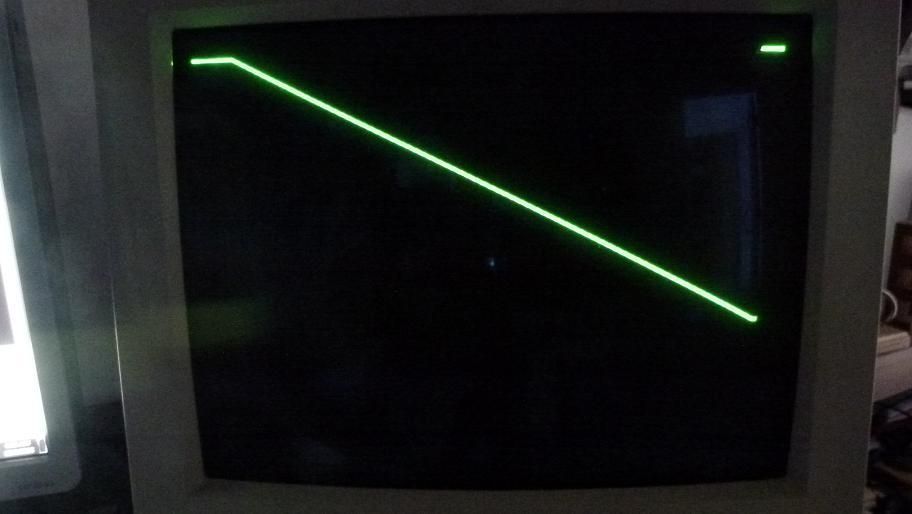

init_state:

if ( vblank & vsync ) begin

x0 <= 0;

y0 <= 0;

x1 <= 200;

y1 <= 300;

if ( x0 > x1 ) begin //negative "/" slope, sx=0

dx <= x0 - x1;

sx <= 1'b0;

end

else begin //positive "\" slope, sx=1

dx <= x1 - x0;

sx <= 1'b1;

end

dy <= y1 - y0; //CPU sending coordinates must follow y1>y0

end

prep_state:

if ( dx > dy ) begin

num <= dx;

end

else

num <= dy;

Hplot_state:

if ( countflag ) begin

if ( y0 < y1 ) begin

num <= num + dy;

e2 <= num + num;

if ( e2 >= dx ) begin

num <= num - dy;

x0 <= sx ? x0 + 1'b1 :

x0 - 1'b1;

X <= x0;

end

else begin

y0 <= y0 + 1'b1;

Y <= y0;

end

end

end

Vplot_state:

if ( countflag ) begin

if ( y0 < y1 ) begin

num <= num + dx;

e2 <= num + num;

if ( e2 >= dy ) begin

num <= num - dx;

x0 <= sx ? x0 + 1'b1 :

x0 - 1'b1;

X <= x0;

end

else begin

y0 <= y0 + 1'b1;

Y <= y0;

end

end

end

endcase

end

endmodule