Design of Parallel Video Board 'Backplane'

- GARTHWILSON

- Forum Moderator

- Posts: 8775

- Joined: 30 Aug 2002

- Location: Southern California

- Contact:

Re: Design of NEW 3.3V Devboard 'Backplane'

Quote:

I post v1.0d at the head because I have a preliminary final design.

http://WilsonMinesCo.com/ lots of 6502 resources

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

-

ElEctric_EyE

- Posts: 3260

- Joined: 02 Mar 2009

- Location: OH, USA

Re: Design of NEW 3.3V Devboard 'Backplane'

GARTHWILSON wrote:

I'm not sure I understand. I see "v1.0a" and "v1.0b" on the board images, but no "v1.0d"...

-

ElEctric_EyE

- Posts: 3260

- Joined: 02 Mar 2009

- Location: OH, USA

Re: Design of NEW 3.3V Devboard 'Backplane'

Work was busy, so I could not do the pin assignments which requires much dedicated 'uninterrupted' time. But I did find an error on the layout, and optimized some routings. Header should be updated soon.

On a side note, I received parts from Digikey for a few 'pass-thru' PVB's using minimal parts. These pass-thru PVB's would potentially be PVB1 thru PVB5... I should spec one of these boards on the PVB thread... I'll be able to catch up Tue&Wed.

On a side note, I received parts from Digikey for a few 'pass-thru' PVB's using minimal parts. These pass-thru PVB's would potentially be PVB1 thru PVB5... I should spec one of these boards on the PVB thread... I'll be able to catch up Tue&Wed.

-

ElEctric_EyE

- Posts: 3260

- Joined: 02 Mar 2009

- Location: OH, USA

Re: K1 Controller board Pin Assignments

Ok, finished the pin assignments for the controller board. Following the traces for each pin led me to one more shorted signal on PVB1. This I believe to be the last error, and the head pic has been updated. I have the funds needed for a board run and will make one tomorrow if nothing else comes up...

- GARTHWILSON

- Forum Moderator

- Posts: 8775

- Joined: 30 Aug 2002

- Location: Southern California

- Contact:

Re: Design of NEW 3.3V Devboard 'Backplane'

There appear to be traces touching pads they shouldn't at pins 17 and 50 of the connectors, but I realize that what I'm seeing might just be round-off errors in the drawing for the small size. Be sure to visually scan both layers individually, blown way up, up and down the rows.

http://WilsonMinesCo.com/ lots of 6502 resources

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

-

ElEctric_EyE

- Posts: 3260

- Joined: 02 Mar 2009

- Location: OH, USA

Re: Design of NEW 3.3V Devboard 'Backplane'

Good eye Garth, they're shorted but pins 17 & 50 are GND on each PVB.

Re: Design of NEW 3.3V Devboard 'Backplane'

This looks wrong to me:

Do you have a DRC checker?

Cheers

Ed

Do you have a DRC checker?

Cheers

Ed

- GARTHWILSON

- Forum Moderator

- Posts: 8775

- Joined: 30 Aug 2002

- Location: Southern California

- Contact:

Re: Design of NEW 3.3V Devboard 'Backplane'

If they're supposed to make contact, I would recommend making the trace head directly into to the pad, so there aren't angles of much under 90° in the copper. My understanding from one of our PCB supplierss' explanation is that it makes it harder for them to get a good yield of reliable boards. Ed's picture shows what could turn out to be a problem. BTW, there's nothing wrong with straying from 0-45-90° trace angles. Make them whatever you need to.

http://WilsonMinesCo.com/ lots of 6502 resources

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

-

ElEctric_EyE

- Posts: 3260

- Joined: 02 Mar 2009

- Location: OH, USA

Re: Design of NEW 3.3V Devboard 'Backplane'

Well, I've tried to keep the GND's in parallel with the high speed clock signal pretty much equidistant, even around bends... EDIT: I will enlarge the copper even more for the types in BigEd's snapshot.

- GARTHWILSON

- Forum Moderator

- Posts: 8775

- Joined: 30 Aug 2002

- Location: Southern California

- Contact:

Re: Design of NEW 3.3V Devboard 'Backplane'

If your CAD doesn't have teardropping, you can zoom way in and add little traces in the corners to accomplish the same purpose. Keeping "equidistant" keeps a consistent transmission-line characteristic impedance (if other things remain equal too), but that in itself is probably pretty meaningless if you're not keeping to a particular value and terminating to that value. You'll still be keeping the signal's return current very closeby which accomplishes much of the desired goal.

http://WilsonMinesCo.com/ lots of 6502 resources

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

The "second front page" is http://wilsonminesco.com/links.html .

What's an additional VIA among friends, anyhow?

-

ElEctric_EyE

- Posts: 3260

- Joined: 02 Mar 2009

- Location: OH, USA

Re: Design of NEW 3.3V Devboard 'Backplane'

Thanks Garth & Ed, I think I may have something worthy of manufacture now. Maybe this one will be without 1 mistake. Updated header pic. I'll be able to polish off the rest of the header tonight when I get home.

-

ElEctric_EyE

- Posts: 3260

- Joined: 02 Mar 2009

- Location: OH, USA

Re: Design of NEW 3.3V Devboard 'Backplane'

Updated...

Time to move on! I'm rolling the dice with this final version. It's in the queue...

Time to move on! I'm rolling the dice with this final version. It's in the queue...

-

ElEctric_EyE

- Posts: 3260

- Joined: 02 Mar 2009

- Location: OH, USA

Re: Design of NEW 3.3V Devboard 'Backplane'

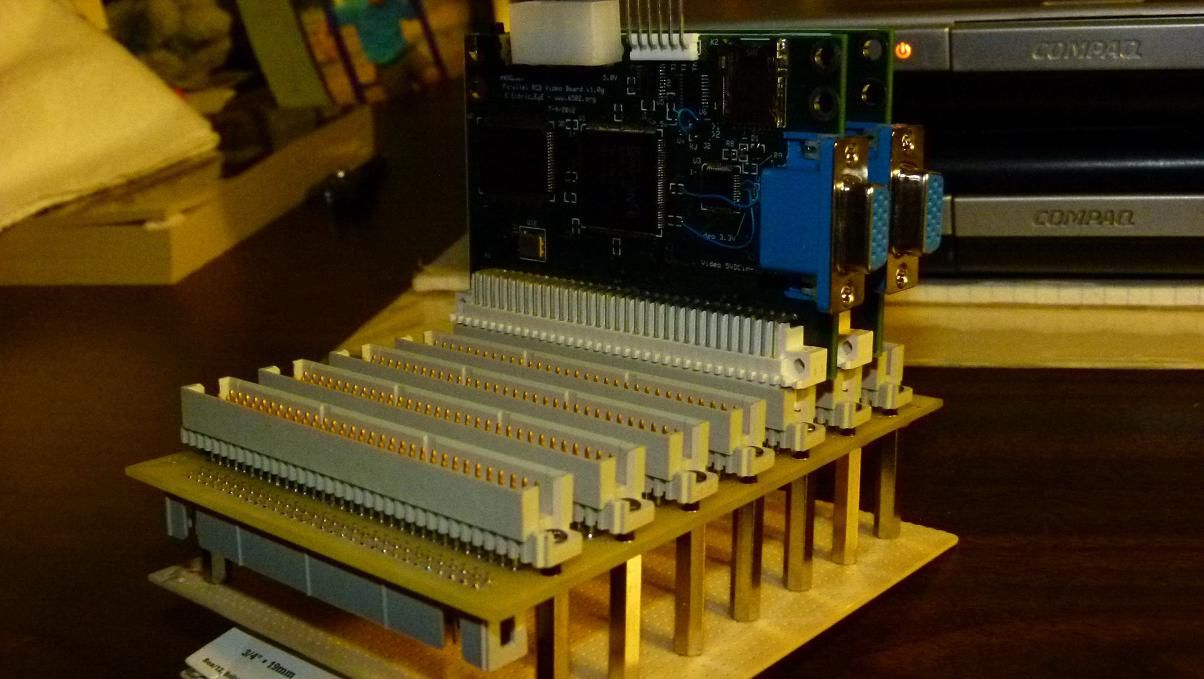

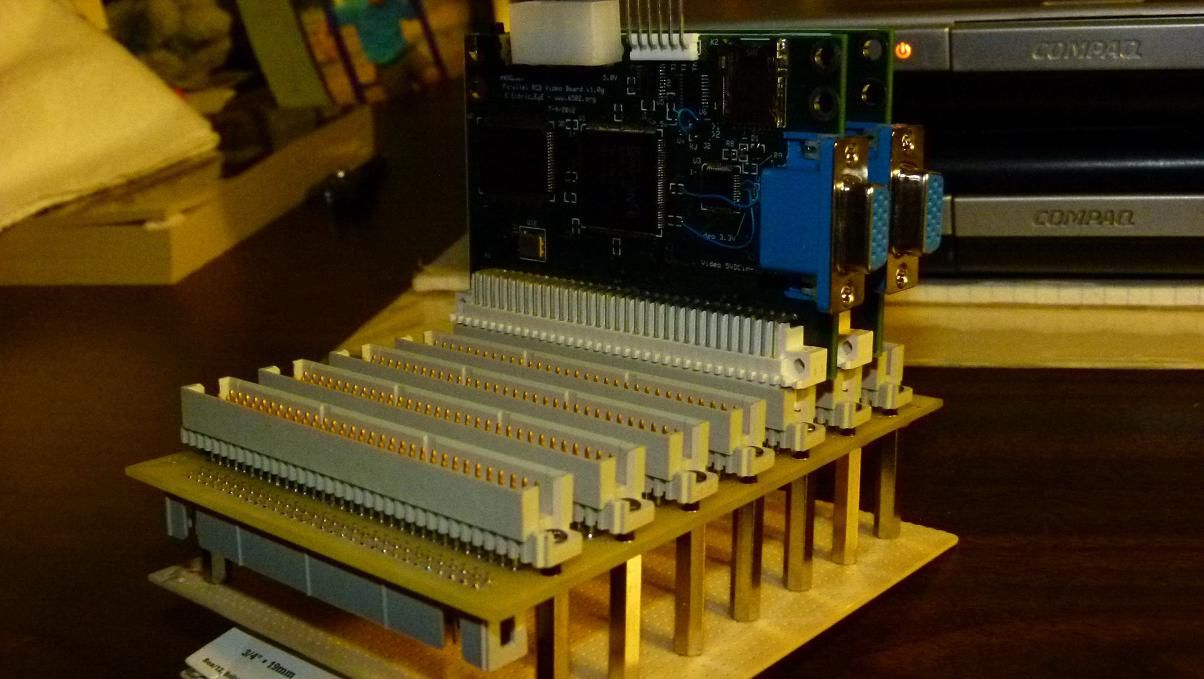

I just received the boards. Tomorrow, I will solder in the receptacles and put together 1 PVB bypass board. Will document how to do this on that thread.

-

ElEctric_EyE

- Posts: 3260

- Joined: 02 Mar 2009

- Location: OH, USA

Re: Design of NEW 3.3V Devboard 'Backplane'

I'm done soldering today. 800+ holes. Will do another PVB board next week.

More form than function at this point...

More form than function at this point...

- BigDumbDinosaur

- Posts: 9428

- Joined: 28 May 2009

- Location: Midwestern USA (JB Pritzker’s dystopia)

- Contact:

Re: Design of NEW 3.3V Devboard 'Backplane'

ElEctric_EyE wrote:

I'm done soldering today. 800+ holes. Will do another PVB board next week.

More form than function at this point...

More form than function at this point...

Sounds like an excuse to devise a wave-soldering station!

x86? We ain't got no x86. We don't NEED no stinking x86!