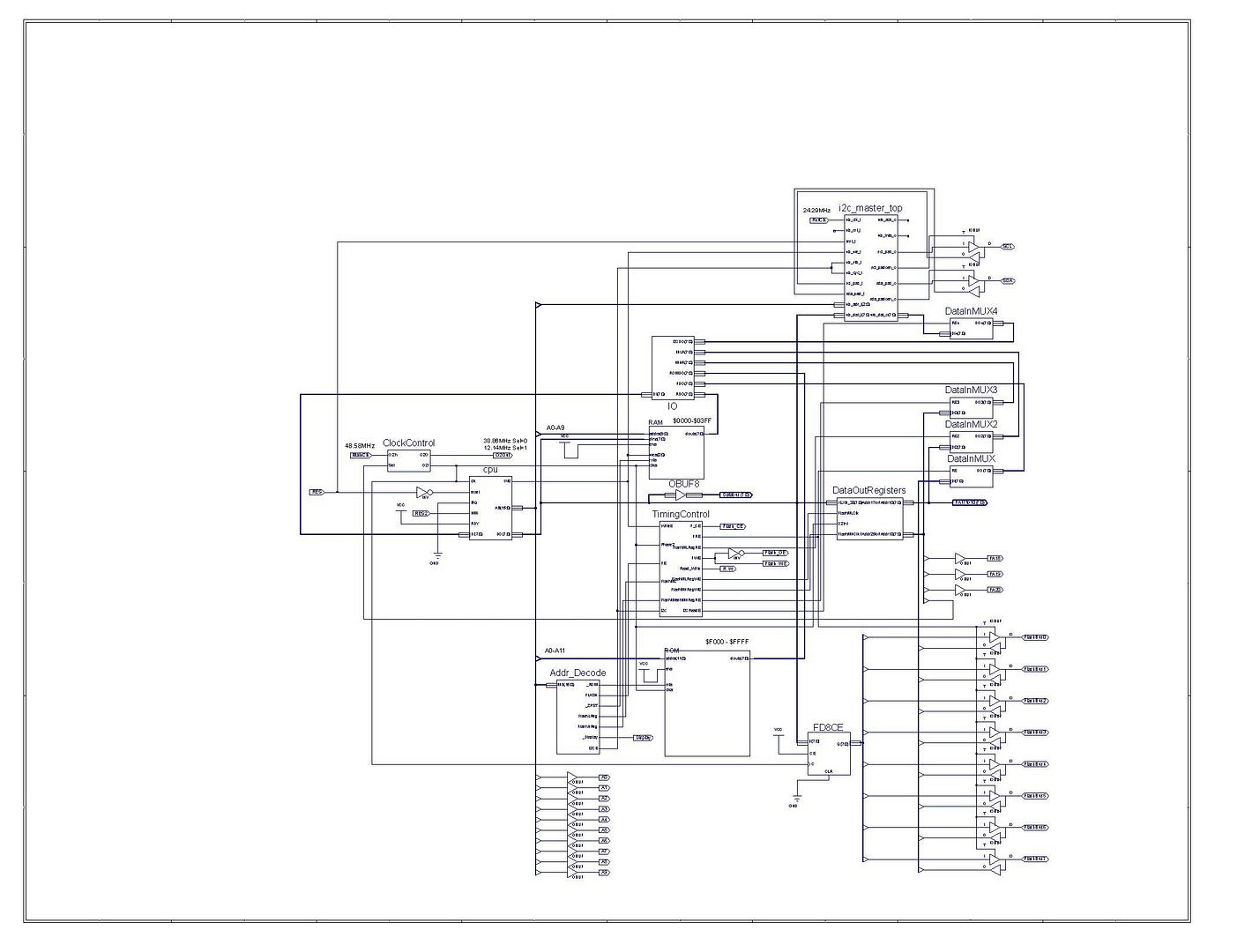

The 6502 core won't go as fast as 97MHz. I also don't have phase 1/phase 2 clocks in my core, just a single clock input...

The cpu would still run @48.58MHz... The 97MHz would run a 2 to 4 bit counter to feed RDY, and would count 0 to X(whatever is needed for each device) on the rising edge (both frequency's would have the same rising edge since 1 is just 2X the other). It would give finer resolution to avoid delaying the CPU any more than absolutely necessary.

...The RDY signal needs to be asserted/deasserted on rising edges of this clock, just like any other input/output signal to the core.

Rising edges, yes. I need to think edges, not levels, especially since FF's are involved.

...Also, don't forget there's an extra cycle delay when the core reads from memory. It presents the address on the AB bus, and on the next cycle, it expects the data on DI.

I have a FF for the Flash RE signal delaying it one cycle. The Flash WE is just logic, no FF.

Actually, the same is true for my 2 Flash bank address registers(A10-A17) and (A18-A20, 5 bits unused). I think I also have the Flash CS delayed one cycle too. I will have to check about the CS when I get home tonight, I have the newest project files on another computer at home. Forgot to update this computer...

__________________________________________________________________________________________________________________________

No, the CS is not delayed. I know this would've screwed up the WE, but at one point I was testing this scenario.