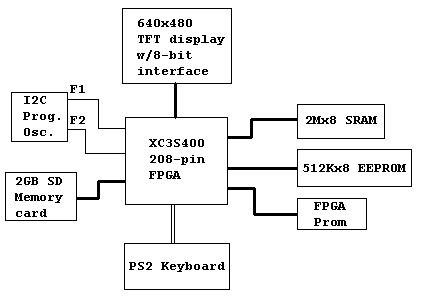

In this thread I would like to attempt at fitting a few more "cores" into a larger Xilinx FPGA, the Spartan 3!:

1) Arlet's 6502 Core

2) A PS2 keyboard interface core

3) An I2C core

4) A USB or SD card Core

All the cores are written in HDL or Verilog. Most will be obtained from opencores.org. I will use a top-level schematic to connect them all. I know the PS2/I2C cores have wishbone I/O interfaces. Will have to search out USB/SD card...

I have graphic software routines, controlled by the PS2 interface, that I've written for my W65C02 controlled PWA project, and would like for them not to go to waste, since I have decided to take advantage of 65816 to replace the 6502 in that project. The routines are meant for a 5.7" 640x480 TFT/LCD NewHaven display. It has an 8-bit display controller built in, which supposedly can run to 50+MHz.

So I thought, this is the perfect time to start this thread. Certain pieces have fell into place to finalize my decisions about the next major step of progress with the PWA, i.e. I've decided to use the 65816. The last piece of software has to be completed for the 6502PWA project is a memory hex dump routine, which I intend to use here as well.

I'll be posting everything: hardware & software here. So you can grill my weak software skills.

Anticipated completion for this "6502SoC" project is 6 months to 1 yr. The goal is simply to use all the Cores with the graphic routines, and of course to see top speed of Arlet's 6502! More details will be exposed, as the thread continues...

Edit: Renamed title. Clarified further.