Finding out what happens in which PHI2 clock cycle inside the envelope generator

can be a bit tricky, and I think I would need to gain some "mental distance"

from the schematics for making a try.

While drfiemost was busy, I tried to dig into the rest of the

SID,

and I think I should post my stuff before some of the details

start slipping from my memory...

;---

Now about the paddle related stuff:

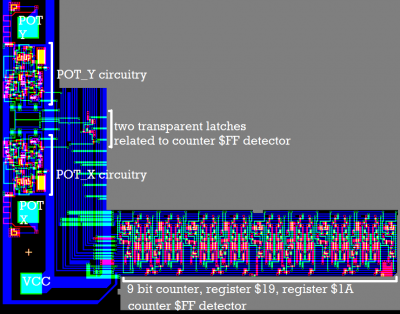

Attachment:

paddle.png [ 128.57 KiB | Viewed 6451 times ]

paddle.png [ 128.57 KiB | Viewed 6451 times ]

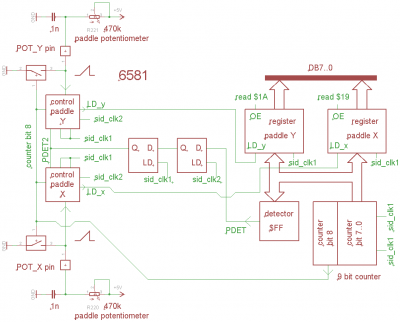

Block diagram:

Attachment:

paddle_block.png [ 23.85 KiB | Viewed 6451 times ]

paddle_block.png [ 23.85 KiB | Viewed 6451 times ]

We have a 9 bit counter running at PHI2 speed.

Bit 7..0 from the counter are fed into two 8 bit latches, POT_X and POT_Y.

At the POT_X pin, we have an external capacitor, which is charged

through the paddle potentiometer resistance to +5V.

When the voltage at the POT_X pin has reached a certain level,

the value from the counter is loaded into the POT_X register.

Also, when the coutner has reached $FF (maybe because the paddle

potentiometer is missing), there is some circuitry that forces

loading the counter value into POT_X.

It's a 9 bit counter, while the counter MSB ( bit 8 ) is 1,

the external capacitor is discharged through a FET in the

SID which is close to the POT_X pin.

Same thing for POT_Y.

;---

So one "conversion" from paddle potentiometer position to POT_X,POT_Y value

happens within every 512 PHI2 clock cycles.

Note, that PHI2 clock frequency is different for a PAL and a NTSC C64.

If the capacitors at the POT_X, POT_Y pins in both C64s would have

exactly the same value (usualy, they haven't),

...

and if the +5V supply voltages in both C64s would be exactly the same

(usually, it isn't),

...

reading out one and the same paddle position on both C64s

probably might give you a value that differs by 4% or such.