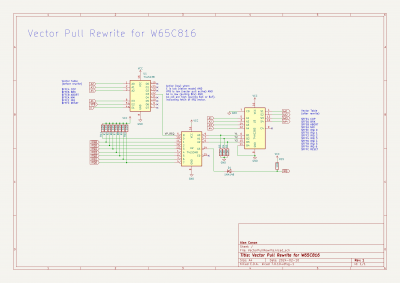

Here's a circuit that adds six more IRQ vectors to the W65C816, for a total of seven, triggered by hardware priority.

The circuit detects when the IRQ vector $FFEE-FFEF is being pulled using a 3-to-8 encoder to detect when E and VPB are low, indicating that an interrupt vector is being fetched in native mode. Additionally A4 must be low (excluding the fetch of the RESET vector at $FFFC-$FFFD), and A3-A1 must all be high (excluding the fetch of the COP, BRK, ABORT, and NMI vectors).

Seven active low hardware IRQ inputs are provided, numbered 0 to 6, with the lower number taking the higher priority. A priority encoder encodes the winning IRQ number, and it is added to bits A1-A3 (with potential carry to A4) by a 4-bit adder. This effectively adds an offset of $00, $02, $04, $06, $08, $0A or $0C, to the vector pull, resulting in a fetch of one of the following seven potential IRQ vectors.

An IRQ output, active low, is provided whenever one of the seven hardware interrupts is asserted.

Code:

$FFEE IRQ 0

$FFF0 IRQ 1

$FFF2 IRQ 2

$FFF4 IRQ 3

$FFF6 IRQ 4

$FFF8 IRQ 5

$FFFA IRQ 6

Attachment:

vpb.png [ 344.04 KiB | Viewed 2510 times ]

vpb.png [ 344.04 KiB | Viewed 2510 times ]