and3rson wrote:

Mind sharing which dual-ported RAM do you use and if it's still in production? I've seen some DIPs on Mouser some time ago, but they all seem to be out of stock now... And it seems like dual-ported RAM is the easiest way to do video, since bus sharing becomes a non-issue.

I wasn't able to find any DIP dual-port RAM in production or for an affordable price. But I did find some (18 of them, to be exact) NOS Cypress CY7C144 8K x 8 Dual Port Static RAM on eBay last year for about $2.30 shipped per IC. They're PLCC, though. UTSource is always a good bet, as Bill (plasmo) says, but I don't think I had heard about them yet when I was dual-port RAM shopping last year.

gfoot wrote:

(Incidentally, 74HC138 and 74HC139 can be fairly easily used as multi-bit comparators, at least for certain bit patterns, instead of wider gates.)

That's a cool idea. I have some AHC `139s too that I use for Ø2 qualification. They're pretty fast.

gfoot wrote:

If you have a two channel oscilloscope that works above 20MHz then it could be good to check how the clock and load signals synchronise in each case (inverter or no inverter), measuring them at the pins of the shift register.

I have an old 200^H^H^H100Mhz 2-channel Tektronix analog scope. (I could have sworn it was a 200MHz one, but the evidence to the contrary is right there in the photos...

) The 25MHz dot clock is sort of just barely within its power, but it looks pretty spiky. It's not so bad that doing what you suggest wouldn't give some useful info though. I'll try to remember to do that tomorrow and take some comparison photos.

Edit: How about now instead? Dinner is taking a while...

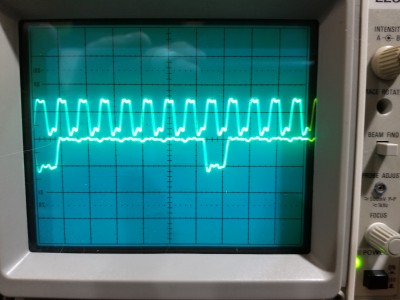

Here's the inverted dot clock compared to the load signal:

Attachment:

inverter.jpg [ 3.15 MiB | Viewed 270 times ]

inverter.jpg [ 3.15 MiB | Viewed 270 times ]

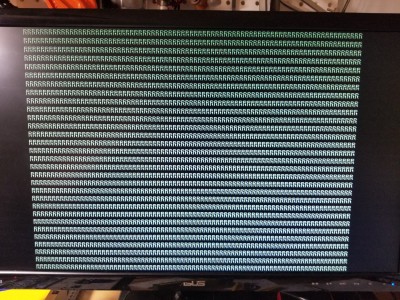

And here's what the output looks like on "Fussy:"

Attachment:

inverter output.jpg [ 6.02 MiB | Viewed 270 times ]

inverter output.jpg [ 6.02 MiB | Viewed 270 times ]

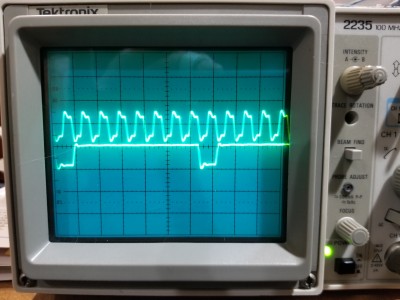

Here's with no inverter:

Attachment:

no inverter.jpg [ 3.23 MiB | Viewed 270 times ]

no inverter.jpg [ 3.23 MiB | Viewed 270 times ]

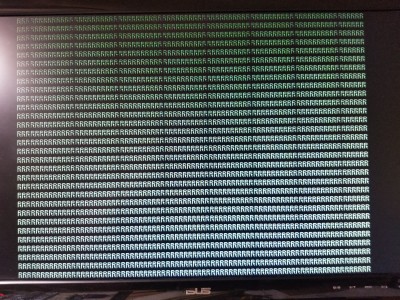

And the output with no inverter:

Attachment:

no inverter output.jpg [ 6.08 MiB | Viewed 270 times ]

no inverter output.jpg [ 6.08 MiB | Viewed 270 times ]

Initially the output was also off by a pixel at the end of each line, but after an auto-adjust that cleared up. Still has those dark vertical bars though; I think you should be able to see them in the photo.

gfoot wrote:

Great to see. Where do VSYNC, VBLANK, and BLANK come from? More counters based on the shift register load signal, maybe going through logic gates to compare against key values? Is BLANK just for horizontal blanking or combined blanking?

They're generated by a timing ROM almost exactly like the one in your "Simplest Video Card." Since I'm not using it for image data, I had 5 spare bits to generate some other signals. I have had HBLANK\ and VBLANK\ since day one, and this week I added BLANK and BLANK\, which are combined blanking signals. I kept wanting them for various things and being forced to provide them with logic; I finally decided they were useful enough to add them to the ROM and ditch the extra ICs.