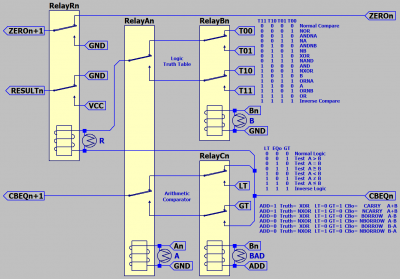

Then lets talk Zero for a moment, cause we need an eight (or nine?) input NOR of the result.

Is 100000000 with CarryOut a Zero? Open collector or drain provides a solution, but not fast.

Fast might be a series circuit in parallel with the final XOR operation (CBT3253 could do both),

but still 6nS+250ps*8+elmo. I got no drawing ready in CBT, only in relays of an old drawing.

Coils and lamps give sneaky free differential XOR, don't go looking for gates or throws.

Attachment:

Relay20221020.png [ 63.39 KiB | Viewed 12908 times ]

Relay20221020.png [ 63.39 KiB | Viewed 12908 times ]

Magnitude comparator chain could compare for equality to zero, but would need to save a

copy of the last testable result for that purpose. Thinking an extra cycle only when Zero is

checked might be less wasteful of time than always compute Zero we may never look at.

Saying a wastefully tested Zero flag replaced by a byte saved for deferred test on branch.

That byte along with saved C4 might be useful for decimal adjusts too.

A tree of 74AS detecting Zero after the final result could take 9nS. Every cycle, weather

we need it or not. AUC might be faster, though a longer tree with fewer inputs per gate.

This sort of Zero doesn't offer any help for the challenge of adjusting decimals.

Is 6502 Zero testable/readable other than by branches?