plasmo wrote:

I think you've done a great job getting to 40MHz at 4V

Thanks! But I probably didn't. Not in a significant way

. I was posting very early this morning whilst being eaten by mosquitoes and sitting in the dark because of being woken by loadshedding. Not a good idea.

The program I had running at 39Mhz was a simple 3 byte jump instruction that I had been using for initial testing. This morning I've retried with the more complex read'y / write'y / index'y / interrupt'y program I've since managed to get onto the pico. It does not run at anything above 36MHz (and sometimes that glitches but 35.5Mhz is stable). Unfortunately I was getting way too excited yesterday and just trying to see how high I could crank the numbers, I wasn't rigorously checking or recording what I was doing.

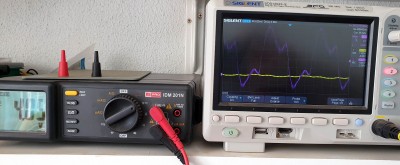

Attachment:

20221205_084302.jpg [ 192.22 KiB | Viewed 780 times ]

20221205_084302.jpg [ 192.22 KiB | Viewed 780 times ]

Here's a picture of the '816 on running at 36Mhz at 4.05V. The clock signal is in purple - the yellow trace is zero. The scale is 1V per div and 10ns per div.

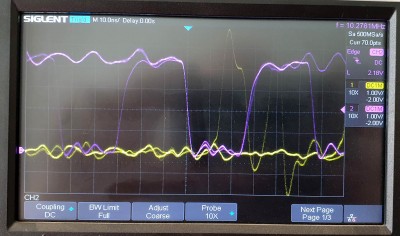

Attachment:

20221205_084929.jpg [ 176.63 KiB | Viewed 780 times ]

20221205_084929.jpg [ 176.63 KiB | Viewed 780 times ]

And another picture of address line 0 in purple and data line 0 in yellow. Honestly the address bus signals are really clean given the mess of noise and wire on my board. The yellow trace (being mostly driven by the Alliance SRAM) could probably be a bit better but it's hard to tell what is real and what is 'scope limitations.

plasmo wrote:

I now have faster RAM (10nS) and fast single-gate buffer so it may be interesting to repeat my overclock experiment. I'm afraid of 10nS RAM! 10nS at 5V is nightmare, so I may need to do

3-D stacking to minimize the wire length. That was something I've done with Z80, more for visual effect than control impedance consideration.

Bill

I'm really looking forward to seeing what can be done with this! Already knowing that the target overclocked frequency I want to use is about half of what can be achieved is quite comforting.

I saw your Z80 stackup way back when you first posted and thoroughly liked it. I still do

but I think if I tried something like that I'd end up with soldering iron in the eye...

(also your post has reminded me I still need to test outside of bank 0.)

Cheers,

Andrew