Programming the 65816 says:

Quote:

The ABORT’ input pin, when it is asserted, causes the current instruction to be aborted. Unlike an interrupt, none of the registers are updated and the instruction quits execution from the cycle where the ABORT’ signal was received. No registers are modified. In other words, the processor is left in the state it was in before the instruction that was aborted. Control is shifted to the ABORT’ vector after an interrupt-like context-saving cycle.

Quote:

A negative transition will inhibit modification of any internal register during the current instruction. Upon completion of this instruction, an interrupt sequence is initiated. The location of the aborted opcode is stored as the return address in stack memory.

Quote:

It should be noted that despite the interrupt's name, an "aborted" instruction isn't actually aborted—all steps of the instruction will be completed before the 65C816 reacts to the interrupt. What is aborted are computational changes to a register and/or memory that the instruction would have made had it not been "aborted."

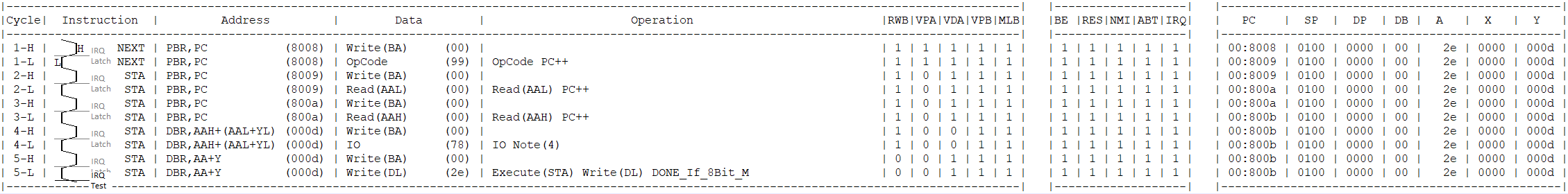

The first would make more sense because I don't see how else it would stop doing memory accesses during the aborted instruction.

The second would make sense because it follows every other interrupts pattern (except reset) of completing the current instruction first before the interrupt occurs. But what if the aborted instruction is a write? Does RWB go high to stop the write? And what about all the addressing reads? Do VPA and VPB go low during the rest of the instruction to indicate memory shouldn't read?

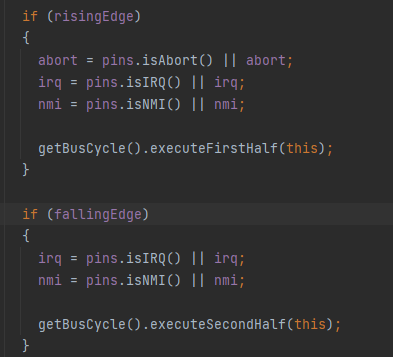

Checking out Sam Falvo's lib65816 isn't helpful because emulation is done at an instruction level, not a cycle level. And Francesco Rigoni's lib65816 is even less helpful as it doesn't handle abort at all.

As always any enlightenment would be most appreciated!