Good news everyone! Another W65C02 is up and running.

After 3D-printing a few wire-wrap sockets (

http://forum.6502.org/viewtopic.php?f=4&t=2029&p=83239#p83238), I was itching to put them to use. I always wanted to wire-wrap a computer - it seems like relaxing activity much like knitting... And I've never put together a

real '02 computer, only FPGA-based, which somehow does not feel real. That's two marks on my bucket list.

The new computer is a subset of Garth's

http://wilsonminesco.com/6502primer/potpourri.html#BAS_CPU (misappropriated by Mr. Eater of googletube), and the board was dubbed

GARTH-1. Thank you, Garth, for a solid, simple design - and the rest of the primer!

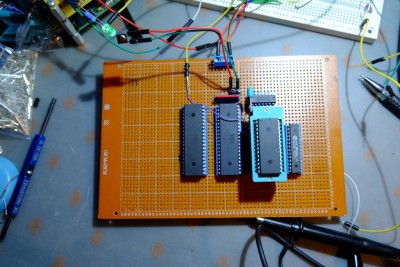

Attachment:

garth-1.top.jpg [ 438.37 KiB | Viewed 795 times ]

garth-1.top.jpg [ 438.37 KiB | Viewed 795 times ]

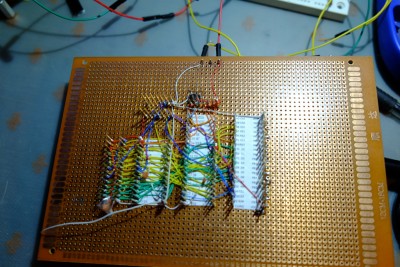

Attachment:

File comment: Bottom wire-wrap view of GARTH-1

garth-1.bot.jpg [ 501.61 KiB | Viewed 795 times ]

garth-1.bot.jpg [ 501.61 KiB | Viewed 795 times ]

Since I lose everything I ever write down sooner or later, I am posting some details, as much for my future self as for anyone interested:

Currently on-board:

CPU: W65C02

ROM: ATM28C256

RAM: UM61m256K-15 (skinny 32K RAM)

IO: W65C22N (I could not find an S in my pile - for some reason I bought a bunch of N's a few years back)

There is a resistor array for all the pullups, and a little header with a microscopic MCP100T SOT23-3 reset supervisor. There is a reset button floating in the air near the LED.

The cheap Chinese ZIF socket works like a charm, but unfortunately, instead of pins, has weird flat tabs that run like this:

l l l l

l l l l

They don't fit into sockets. I finally found a female header that took them, so the structure is now 3-stories high. But it works.

ClockingI don't have a proper clock yet as all my oscillators seem to be in the tens of MHz from my FPGA days. In the meantime I've been using an Daryl's SBC4 to bang out the clock for its little brother (the LED you see is actually the clock, with a little wire to clock GARTH-1). I am running tests at around 500KHz.

Build notes:Overall, the build took a day and a half (largely due to my disorganized space and time wasted looking for various chips and caps...). Wire-wrapping is not quite like knitting as you really have to pay attention to each individual connection, by the way. But very pleasant, and oh so retro, especially with appropriate period music. I finally got to use the little roll of Kynar wire I bought as a teenager and managed to not get rid of, somehow.

I started with the CPU and a NOP-generator stuck into the RAM socket. After banging on the knobs of my broken Kukusui 20MHz scope (the traces seem to move up and down on their own, and break up into spectacular patterns, not very helpful in debugging) I figured that it probably works. I added a ROM and loaded a simple dead loop at $FF00, which let me check the address bus lines. I then added the RAM, and burned a ROM with a simple test that JSRs into the RAM which promptly RTSs to the stable dead loop at $FF00 for verification.

Finally I added what I thought was the 6522 (but was a 6521!), and wasted half a day debugging every component, removing everything and going back to the NOP generator... Eventually I slapped my forehead and put a real 6522 in, and blinked some LEDs.

Software developmentI use Linux, of course.

I use the 64TASS assembler, outputting a 64K binary. I then run dd to trim off the low 32K. It's a good thing I can use dd - otherwise I would have to wait for Balena Etcher people to hire 10 more people and make another award-winning 80MB application! There is probably a better way to generate the binary image of the upper 32K, but I haven't found it yet.

I then burn the EEPROM using my $50 XGecu Pro and minipro open-source software.

Here is my Makefile:

Code:

default:

64tass test.asm --flat --list=test.lst --labels=test.lab -o test.bin

dd if=test.bin of=test.32k ibs=32768 skip=1

burn:

minipro -p AT28C256 -w test.32k

clean:

@rm -f *.hex *.lst *.out *.lab *.bin *.32k

@echo "Clean!"