Attachment:

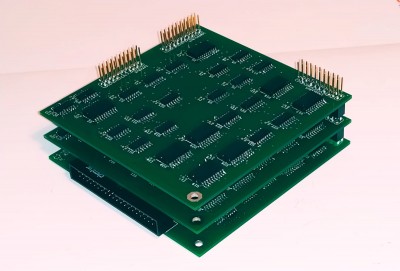

WhatsApp Image 2019-10-06 at 16.28.40.jpeg [ 111.62 KiB | Viewed 1769 times ]

WhatsApp Image 2019-10-06 at 16.28.40.jpeg [ 111.62 KiB | Viewed 1769 times ]

Attachment:

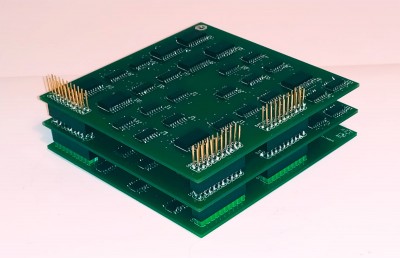

WhatsApp Image 2019-10-06 at 15.01.56.jpeg [ 108.64 KiB | Viewed 1769 times ]

WhatsApp Image 2019-10-06 at 15.01.56.jpeg [ 108.64 KiB | Viewed 1769 times ]

Finally, B1 and B2 are completed and they.... kinda work... Although I'm going to have to check quite a few things.

Remember how B0 performed flawlessly, both when connected via the expansion port, and when replacing CIA#2? Well, that's no longer true. I'm getting weird image artifacts when doing that, even using only B0. All registers work OK when connected into the expansion port, so it seems something's wrong with the port outputs. Until I figure it out, I'll do only testing via the expansion port.

Now, about the new boards, I've only been able to do some limited testing. Timers start and stop, and the do count as expected. B0+B1 work, B0+B2 work too. However, if I connect the whole stack (B0+B1+B2) my C64 starts to behave weirdly. I get no cursor and no keyboard. This implies CIA#1 no longer works. I get the startup screen, and Run/Stop+Restore does what it should, so CPU, VIC.. they are pretty much OK. I may be drawing too much power and CIA#1 is the first victim, or some other signal may be being affected.

Something I didn't take into account is how many inputs can I drive from the C64 outputs, and I'm maybe paying for that now.

So, plan for the next couple of weeks. Run some extensive testing on both timers individually, identify why B0 seems not to work properly on its own, and find what's going on when I connect the full stack.

After an uninterrupted successful streak of 14 months, with no issues at all, this feels weird but... It couldn't be so easy

Cheers!