Hello everyone!

After the Christmas break, I have a few updates!

I will start with the very last fix I've implemented. Let's see what past-me said :

past-daniMolina wrote:

past-past-daniMolina wrote:

- On powerup (or reset) TOD should not be counting, but it is. A write to the tenths register starts the count, a write to the hours register stops the count. On my design, TOD is and-gated with a signal I've called COUNT.

The idea was... when /RES goes high, that became a clock pulse for the flipflop that generates COUNT. With its Data pin tied to GND... on reset, COUNT should be 0. Right? Nope. Wrong. As I'm forcing a write to all registers on reset, /LOADT and /LOADH are active, so both /SET and /RESET inputs to the DFF are asserted simultaneously. When the /RES, /LOADT and /LOADH finally goes high, COUNT is always 1.

This will be fixed by taking /Q as COUNT, and swaping /LOADT and /LOADH on the flipflop.

The design was, after all, correct. The data input to the FF was floating so... Fix this, and COUNT is working now as expected.

Well. No. All past-me's were wrong. I now have two full units, which go by the names of U1 and U2. U1 indeed works as expected, but U2 didn't. No matter what I tried, TOD was counting after reset. I was starting to think that asserting both /SET and /RESET was not a very good idea, as any slight delay in the signals could mess with the outcome. I tried replacing the 74HC74 and, not so surpringly, I got different behaviours with different brands. Bad design!

I inserted a new DFF (I had a spare on board) to delay the /LOADH signal to the flip flop by 1 cycle so, in the event of both /LOADT and /LOADH being active at the same time (Which, btw, only happens during reset) /LOADH would be one cycle late, keeping TOD stopped, as expected.

And yes, now, the design is correct, and works as expected. Always. Yay!

In the meantime, I had to resolder a handful of ICs on U2/B4. I might have been a bit over-excited as this was the last board, and I make a lot of mistakes there. But... in the end... brace yourselves for a nice photoshoot!

Attachment:

Real OLD.jpeg [ 138.47 KiB | Viewed 2252 times ]

Real OLD.jpeg [ 138.47 KiB | Viewed 2252 times ]

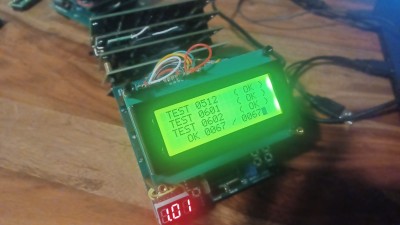

This is a real OLD 6526 passing all tests on my SBC.

Attachment:

Real NEW.jpeg [ 131.34 KiB | Viewed 2252 times ]

Real NEW.jpeg [ 131.34 KiB | Viewed 2252 times ]

Same for a NEW 6526. Of course, nothing can be seen here. If you want to revisit the differences between OLD and NEW CIAs,

here are my findings.

Now, for the real fun.

Attachment:

U1 in OLD mode.jpeg [ 154.79 KiB | Viewed 2253 times ]

U1 in OLD mode.jpeg [ 154.79 KiB | Viewed 2253 times ]

U1 in OLD MODE

Attachment:

U1 in NEW mode.jpeg [ 157.66 KiB | Viewed 2253 times ]

U1 in NEW mode.jpeg [ 157.66 KiB | Viewed 2253 times ]

U1 in NEW MODE

Attachment:

U2 in OLD mode.jpeg [ 123.66 KiB | Viewed 2253 times ]

U2 in OLD mode.jpeg [ 123.66 KiB | Viewed 2253 times ]

U2 in OLD MODE

Attachment:

U2 in NEW mode.jpeg [ 120.13 KiB | Viewed 2253 times ]

U2 in NEW mode.jpeg [ 120.13 KiB | Viewed 2253 times ]

U2 in NEW MODE

The failed test on both U1 and U2 in NEW MODE, is the TOD interrupt test. There's a few cycles difference I can't yet explain. However, this is only evident when I am ticking TOD programmatically, so, instead of 60 times per second (or 50) I can do it at will. When I am counting real time, 4 cycles is not going to matter.

This does not prove my design to be cycle exact. I am only testing for regular situations, and I am not aiming at edge cases. The VICE Test suite will take care of that.

One of the things I fixed on U2, was a dead short to VCC on a few ICR signals. I am hoping this is what was preventing my C64 from booting up!

Today, February 9th, 2024, I do have two full 74HCT6526 working. And it only took me five and a half years!

What's next then? Of course, time to torture my C64 again. If it boots with both 74HCT6526s installed, it has plenty of testing to do.

Also, as my SBC6526 takes two 6526s, I will plug both there, and crank up the speed. Can't wait to see how high they can go!

oneyearago-daniMolina wrote:

PD. So close... I am so close!

And now, I'm already there

But the best is yet to come!

Oh, and by the way, a new release to github with this last few fixed will be uploaded shortly.

Cheers!