I wrote:

the address bus is not guaranteed to contain valid content until Ø2 goes high.

BigDumbDinosaur wrote:

The timing diagram unambiguously shows that RWB, MLB, VPB, A0-A15, VDA and VPA are valid and stable prior to the rise of Ø2, specifically, no more than tADS nanoseconds after the previous fall of Ø2.

Hmm -- I was flummoxed by this remark, but now I realize that imperfectly precise wording on my part opened the door to something other than the point I was driving at.

BigDumbDinosaur wrote:

Unfortunately, WDC based the address setup timing on the (previous) fall of the clock. When I first decided to build my POC unit, I was struggling to get my head wrapped around this. It seemed more logical to quote timing on what was about to happen with Ø2, rather than what had already happened.

Arlet wrote:

That's because they describe what the hardware does. The outputs are probably registered on the falling clock, and tADS is the delay of the output flipflops plus the pad to pin delay. On the other hand, there's no relationship to the next edge, so they can't specify that.

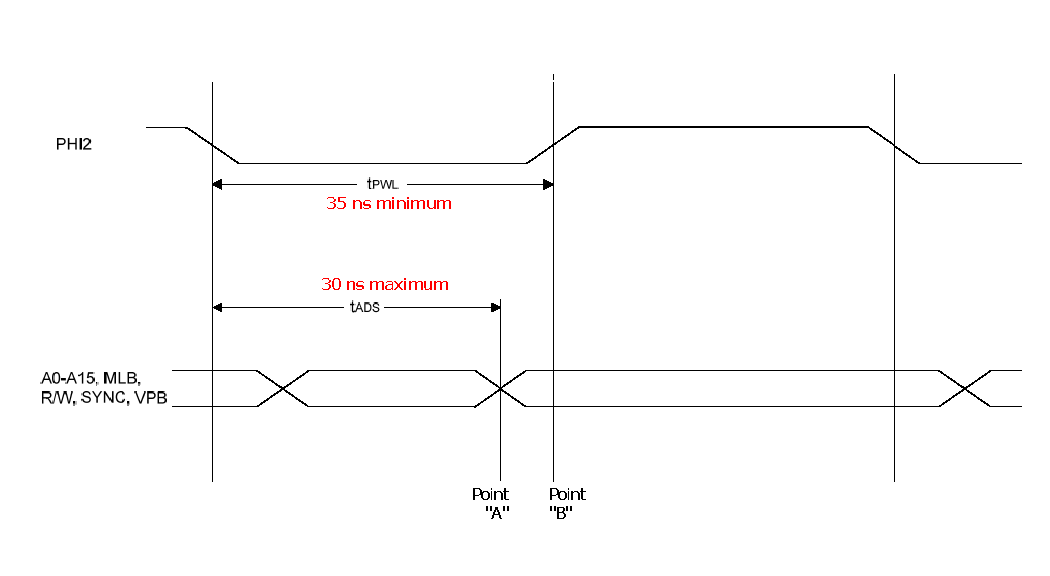

Right. I've marked up part of the '02 timing diagram (below) to illustrate. When the valid address appears at Point A, it's the result of the fall of Ø2 which occurred previously. IOW the valid address doesn't appear "in anticipation" of Point B in future when Ø2 is expected to rise. Hardware can't anticipate something that hasn't happened yet. I could clarify my quote at the top of this post as follows. "The address bus will already contain valid content by the time Ø2 goes high because presumably the clock source keeps tPWL within spec, and

even at its minimum, tPWL will be longer than the maximum tADS delay produced by the CPU."

Attachment:

PHI2 and tADS.png [ 11.24 KiB | Viewed 854 times ]

PHI2 and tADS.png [ 11.24 KiB | Viewed 854 times ]

Returning to the actual, original cause of my quibble, I believe Banedon was asking why we qualify RAM write-enable with Ø2. As I explained in my

post Thursday, the answer is...

If you write-enable RAM or I/O while Ø2 is still low the target device will see an

address bus that is in a state of flux -- not

BigDumbDinosaur wrote:

If you write-enable RAM or I/O while Ø2 is still low the target device will see a data bus that is in a state of flux.

However, the following is correct:

BigDumbDinosaur wrote:

If you remove the 65C816-specific outputs from the discussion you are looking at essentially the same timing model as that of the 65C02.

When running near maximum speed, '02 systems and '816 systems both take almost all of the Ø2-low time to produce a valid address; prior to that the address is garbage. And for write cycles they take almost all of the Ø2-high time to produce valid write data; prior to that the write data is garbage -- and that's normal; static RAM and 65xx peripherals can tolerate that, even though write-enable is asserted throughout the period of flux.

-- Jeff

_________________

In 1988 my 65C02 got six new registers and 44 new full-speed instructions!

https://laughtonelectronics.com/Arcana/ ... mmary.html