Dave has unwrapped a new revision of firmware for the Matchbox Copro, with a memory banking scheme. It would be good to get feedback on the approach, which is readily extendable to 2MByte.

The context is a memory map with just one 256 byte page of I/O, and 64k of RAM, which is the normal map for an Acorn/BBC Micro second processor. (The top 2k of RAM are overlaid at reset time with ROM, and the ROM contents copied into the RAM with the ROM then mapped out again.)

The physical implementation we have is the

Matchbox Copro, a small board by

Jason Flynn with an LX9 FPGA, two pseudo-static RAM chips, power regulation, and level conversion for attaching to a 5V host bus. (Normally that bus would be the

Tube connector on an Acorn micro - it's the 6502 data bus, some control lines, some address lines.)

We took

a simple approach:

- Added 8 registers in page FE to control the paging, with an 8k page size.

- Each 8k slot can then be mapped, either to one of the 8 pages of fast on-chip block RAM or to one of 128 pages of slower off-chip RAM.

- The two I/O devices in the $FE00 area remain as I/O at all times.

- Re-mapping slot 0 or slot 7 works the same as any other slot but needs care and attention because it will affect page zero, the stack, the vectors.

- The initial mapping uses just the fast on-chip block RAMs.

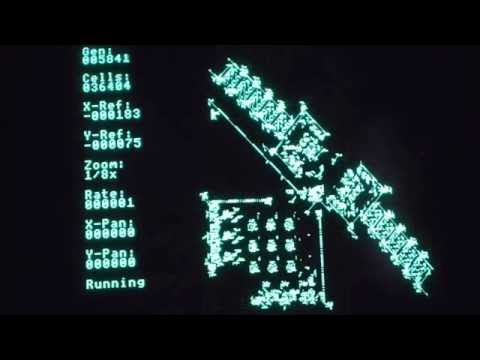

As a demo and a driver, Dave ported a Life program to this platform and we're

able to run a large pattern (almost certainly for the first time on a 6502) - a

Turing Machine:

Although the matchbox physically has 2MByte of (pseudo-static) RAM, it's not byte-accessible without a tad more effort, so we use only half of it. It wouldn't be hard to add another 120 pages of slower RAM, probably at the cost of an extra cycle of access time.

At present the Matchbox runs up to 64MHz with a 65C02 version of Arlet's core.

Several other MPUs are also supported but this mapping story presently only applies to the 6502.