Wow everybody. I have been so engrossed trying to work out what the BEEP is going on that I didn't come back here to see if anyone else had replied - and you have. I am much obliged.

Some reples to your questions and suggestions:

I have been using the serial output to show errors. I'll come back to what I have found below.

NoICE is a Windows program that interfaces with a, I'll call it a monitor program on the 65C02 (and many other chips). The results are displayed on the screen and you can (amongst MANY other things) type into memory and get a response back keystroke by keystroke.

NoICE link:

https://www.noicedebugger.com/ and

https://www.noicedebugger.com/targets.htmlLink direct to the 6502 NoICE page:

https://www.noicedebugger.com/help/targets.htm#65C02I have spent a

considerable length of time checking every connection - not just simple continuity, but checking the resistance is negligable - from pin to pin on the chips - also checking every connection ONLY goes to where it is meant to go as well. Thats a lot of checks! I thought I had it when I found a tiny curl of wirewrap wire loose under a load of connections ... but no.

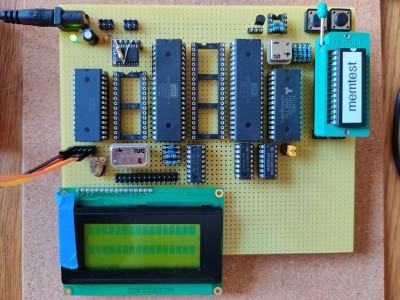

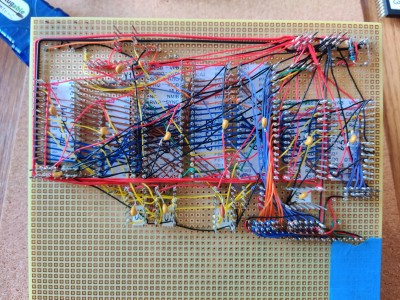

Photos are attached.

Other things I have done (from memory)

1. Replaced the memory chip... then...

2. Replaced all other chips. 65C02 down to 74 series.

3. checked power supply voltage and ripple etc. V a little high - 5.15V. Ripple very good - well, I think so.

I did write the memory test program and it indeed threw up more questions than it answered. Firstly, I think the recurring pattern of bad addresses were down to NoICE itself encountering memory problems in its own date area. Sometimes it will crash, sometimes other effects. I have stopped trying to use it as it is likely to cause confusion.

The memory test program simply fills memory (page 0 and page $02-$7E) with the same value, then it reads it all back and reports (over serial) which addresses don't match. Then it increments the value by 1 and repeats. So it fills memory and checks it with all 0 and then all 1 and so on (wraps back to 0) and repeats infinitely.

What this shows is that every few minutes an address is not written (or not read) correctly. Roughly 5 to 20 errors an hour.

In my ignorance, this implies some sort of timing error or interferance error. I can't see why it should be a timing error. I am only running at 1 MHz and the maximum propagation delay in the glue logic is only of the order of 50ns or so - I think.

As for interferance/crosstalk etc well, I can detect ripples in most address and data lines at clock frequency. They are there but not bad (that is a dangerous statement I guess - my 'scope is, lets say, "not the best". So, I should perhaps change that statement to "they are there and I don't THINK they are too bad").

Okay, so now to construction. This machine is built on a piece of, I think its called perfboard(?). It has a pad round each hole on one side (that I have simply ignored). It therefore has no ground plane. Because of this I decided to connect each power and ground pin to TWO power distribution places one in the north east and one in the south west of the board and also connect every power and ground to its neigbor chip - so that gives a total of three connections for power and ground to each chip. I took Garth's suggestion of making like a spider's web to heart.

Garth, this is actually my second iteration of this board. The first had "swoopy" connections and was so ugly - and wouldn't run anyway - that I started again and did everything "shortest path" and straight.

CountChocula

Hello! I do have a test harness socket that allows me to monitor what's going on at a deep level - uses a good old Arduino to monitor a single stepped machine - but since the problem (or at least the manifestation of it with the memory test program) seems to have changed somewhat - I don't think it would really be possible to step through trillions of instructions. I did think of doing it but I don't think it would be practical.

"Removing every chip I don't need". From photos, you will see I have done this. In fact I had all but a single 6551 support chip out at one stage. No luck I am afraid.

So, where does that leave me? Well, I have ordered - from the USA - a new Twin Industries 8100 series (single ground plane) board as recommended by Garth and when it arrives I will- very probably - start again. In the meantime I will keep troubleshooting but with a) my equipment and b) my lack of knowledge/experience I suspect I am close to the limit of what I can do to find the problem.

GaBuZoMeu, you said about using Phi2(out) (p39) for timing and driving the I/O parts. I will have to get my head round that one. I havn't seen it done in any designs I have come across.

Some notes on the pictures. The odd thing near top left with a resistor soldered across it is an r2c attached real time clock. Connected to one of the VIAs. its not shown on the schematic. The display is not shown either also connected to VIA1

The sets of posts extreme top right and bottom left (back view) are for power distribution. As mentioned above all (well, most) chips' +V and GND are connected to both of these. The distribution posts are connected via the black and red wires along the top and down the left hand side (on the back view).

Oh and I have only connected to pin headers on 1 each of the 6551 and 6522 chips - If I ever get it working I will complete the I/O connections

Attachment:

IMG_20221030_133604.jpg [ 1.8 MiB | Viewed 775 times ]

IMG_20221030_133604.jpg [ 1.8 MiB | Viewed 775 times ]

Attachment:

IMG_20221030_133634.jpg [ 2.51 MiB | Viewed 775 times ]

IMG_20221030_133634.jpg [ 2.51 MiB | Viewed 775 times ]