Progress continues to put the 65Org16.b (16-bit NMOS6502 without decimal mode) into action. 65Org16.a is BigEd's original creation based on Arlet's Verilog NMOS6502 softcore. Arlet & BigEd both continue to refine their work on GitHub, as I do when I find time. I would like to add a 65Org16.c core soon, which would have some simple but excellent time saving opcodes, like

PHX,PHY,PLX, and PLY. I'll revisit that thread when I get most of this other stuff sorted out...

Currently I'm working on I2C drivers. Also, when I hit a roadblock I'm trying to

sift out 1 of 3 6502 Assemblers/Disassemblers (Micromon-64, SuperMon-64, and Hashmon) that will reside in the FPGA BRAM. Looking at the code of all 3, I'm trying to determine all the JMPs/JSRs outside of the code. Looking and comparing the binaries reconstituted through MK's assembler, together with the book 'Mapping the 64', I should be able to make a choice soon.

V1.0 was a failure because the SDRAM layout was incorrect. Took 2 months for that initial iteration. From that version I learned that the MCP2200 appears to function properly with the Br@y terminal working under Windows, when it is fed 10MHz. I say "appears" because I could only look at the transmit and receive LEDs. I really had no drivers for any output devices. This was another shortsighted design error of V1.0...

Enter V1.1:

It's taken an additional 2 months, but I've added a 800x480 TFT touchscreen display interface connector, an I2C touchscreen controller IC and connector, narrowed the traces to .006", added 3 I2C programmable oscillators for 3 IOB's and changed the CS4954 video interface to I2C from parallel. Also the 100MHz clock now goes to all 4 IOB's.

The display I've chosen is a

step-up from a similar display I've used successfully with Xilinx FPGA's in my 6502SoC. I was limited to 38MHz in that design, and expect to be limited here as well because it uses the same 8-bit SSD1963 controller and uses Phase 2 as the clock source. This is

good because I can recycle the software I've written for the display with some minor changes, but it's

bad because the CPU core has the ability to run faster than 38MHz. However, the display is really only being used to make and test drivers. The top_level schematic design is very similar to one of the

last posts on the 6502SoC.

Unlike the 6502SoC though, this V1.1 of the DevBoard is almost all HDL. 3 files are schematic based, 2 address decoding files and the Top_Level schematic. Ideally I would like to convert the 2 address decoding into verilog, like I

converted my ORs module.

Here's the Memory Map:

Code:

65Org16 V1.1 DEVELOPMENT BOARD MEMORY MAP

$0000_0000 - $0000_03FF....................HESMON/OS VARIABLES

$0000_0400 - $0000_07FF....................VIDEO MATRIX (40x25)

8K $0000_0800 - $0000_1BFF....................EXTENDED VIDEO MATRIX (100X60)

$0000_1C00 - $0000_1FFF....................AVAILABLE ZERO PAGE AS FPGA BLOCK RAM

56K $0000_1000 - $0000_FFFF....................UNUSED - REMAINDER 65Org16 ZERO PAGE

60K $0001_0000 - $0001_EFFF....................UNUSED - REMAINDER 65Org16 STACK

4K $0001_F000 - $0001_FFFF....................AVAILABLE STACK AS FPGA BLOCK RAM

4.3GB $0002_0000 - $FFFE_FFFF....................UNUSED

$FFFF_0000 - $FFFF_0007....................I2C REGISTERS

$FFFF_0008 - $FFFF_0009....................PS2 REGISTERS

$FFFF_000A - $FFFF_000D....................SPI REGISTERS

48K $FFFF_OOOE - $FFFF_000F....................UART REGISTERS

I/O $FFFF_0010 - $FFFF_0011....................TFT REGISTERS

$FFFF_0012.................................16-BIT PSEUDORANDOM NUMBER GENERATOR (READ ONLY)

$FFFF_0013 - $FFFF_001F....................UNUSED DECODED

$FFFF_0020 - $FFFF_BFFF....................UNUSED

$FFFF_C000 - $FFFF_CFFF....................HESMON

$FFFF_D000 - $FFFF_DFFF....................OS,DRIVERS,CHARACTER PIXEL DATA

16K $FFFF_E000 - $FFFF_FFF9....................AVAILABLE SYSTEM MEMORY AS FPGA BLOCK RAM

$FFFF_FFFA - $FFFF_FFFB....................NMI VECTOR

$FFFF_FFFC - $FFFF_FFFD....................RESET VECTOR

$FFFF_FFFE - $FFFF_FFFF....................IRQ/BRK VECTOR

8:51 AM 1/7/2012

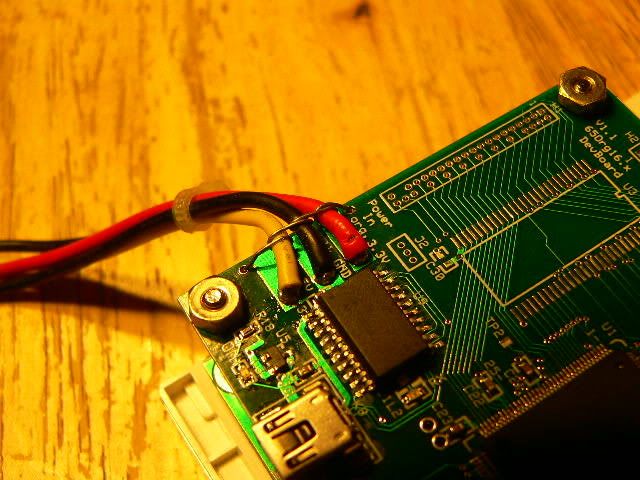

Here are some pics of the construction. No soldering errors this time!

Errors: Silkscreen is covering where I wanted to solder main power wires, but those wires have been secured the way I've envisioned!

I've used 3M double sided tape on a V1.0 board and use it as a mount for the V1.1 (on top) with some vertical standoffs to position it to make room for the PS2 keyboard connector that is shown on the left, on the bottom. Also in the forefront, is the 4-pin .5mm FFC, for the touchscreen panel, and the 20-pin 1mm FFC cables and connectors, for the TFT display.

Here you can more clearly see the interconnections. The small board on the bottom right, with 2 wires going in on the left and 2 wires going out, is the

DC-DC converter for the LED backlight driver for the TFT. I initially tried 3.3V in, but it was using large amounts of current as it was dragging the 3.3V supply down to 2.5V. Thankfully no damage was done to the board.

This is my parts list to date. Most have been copied over from V1.0, so it is still not up to date for V1.1 as it is still under development. But all the IC's that have been planned for on the circuit board are listed...

Code:

65Org16.x V1.1 Development Board Parts List (6/8/2011-12/2011...)

QTY Price Description Part# Package Supplier Sch. ID

1 $6.95 FPGA Prom XCF04S 20-pin TSSOP Digi-Key U2

1 $18.63 FPGA XC6SLX9-3TQG144I 144-pin QFP AvnetExpress U1

1 $7.38 Video Controller CS4954 48-pin QFP AvnetExpress U4

1 $5.23 16MBx16 SDRAM 167MHz MT48LC16M16A2P-6A:D 54-pin TSOPII AvnetExpress U3

1 $1.24 8Mb SPI Flash SST25VF080B-80-4I 8-pin SOIC Digi-Key U10

1 $0.81 3.3V POReset Supervisor DS1818R-10+CT-ND SOT-23 Digi-Key U5

1 $0.74 2.5V 1A VRegulator MCP1826S-2502E/DB-ND SOT-223-3 Digi-Key U7

1 $0.74 1.2V 1A VRegulator MCP1826S-1202E/DB-ND SOT-223-3 Digi-Key/Mouser U8

1 $4.02 100MHz 3.3VOsc. HCMOS/TTL CTX318LVCT-ND SMD Digi-Key U6

1 $2.12 USB to UART MCP2200-I/SO-ND 20-pin SOIC Digi-Key U9

3 $6.75 touch screen controller 296-14340-1-ND 16-pin TSSOP Digi-key

3 $? 3.3V 4kHZ-66MHz Prog Osc DS1085LZ-5+T 8-pin SOIC

3 $0.76 1ea 22uF 6.3V capacitor 445-1595-1-ND 1210 Digi-Key C33,C34,C35

2 $0.53 1ea 4.7uF 10V capacitor 587-1379-1-ND 1210 Digi-Key C31,C32

5 $0.74 10ea .1uF 6.3V capacitor 709-1009-1-ND 0603 Digi-Key C1-C30,C36-C42

5 $0.06 10ea .01uF 16V capacitor 490-1525-1-ND 0603 Digi-Key Alternate to .1uF

1 $0.16 10ea 470nF capacitor 490-1548-1-ND 0603 Digi-Key C43

6 $0.02 1ea 0ohm resistor jumper P0.0GCT-ND 0603 Digi-Key J1-J4,J10

3 $0.02 1ea 100ohm resistor P100GCT-ND 0603 Digi-Key R1-R5,R10,R11

2 $0.02 1ea 75ohm resistor P75GCT-ND 0603 Digi-Key R6,R7,R12

2 $0.02 1ea 300ohm resistor P300GCT-ND 0603 Digi-Key R6,R7,R12

2 $0.56 1ea 5K trimpot 3302W-502ECT-ND SMD Digi-Key R8,R9

3 $0.02 1ea 330 resistor P330GCT-ND 0603 Digi-Key R13,R15,R16,R17

2 $0.02 1ea 4.7Kohm resistor P4.7KGCT-ND 0603 Digi-Key J5,J6,R19,R20

1 $0.02 1ea 3.9Kohm resistor P3.9KGCT-ND 0603 Digi-Key R14

1 $0.02 1ea 470ohm resistor P470GCT-ND 0603 Digi-Key R18

1 $0.56 1ea blue LED 160-1647-1-ND 0603 Digi-Key L1

1 $0.52 1ea green LED 160-1435-1-ND 0603 Digi-Key L2

1 $1.10 RCA Jack Blue CP-1404-ND r. angle thru-hole Digi-Key K6

1 $1.41 6-pos mini din PS/2 CP-4060-ND r. angle thru-hole Digi-Key K5

1 $1.29 4-pos mini din S-Video CP-2240-ND r. angle thru-hole Digi-Key K3

3 $2.99 40-pin .050 male header 609-3724-ND H1-3 mating adapter Digi-Key future

3 $4.41 40-pin .050 female recep 609-3766-ND thru-hole Digi-Key H1,H2,H3

1 $0.69 mom push switch white SW415-ND SMD Digi-Key S1

1 $0.69 mom push switch yellow SW416-ND SMD Digi-Key S2

1 $0.63 6-pin .1 male SIP A1918-ND r. angle thru-hole Digi-Key K2

1 $1.98 1ea mini USB A31727CT-ND SMD Digi-Key K8

10 $0.20 .050" jumper S9014E-03-ND thru-hole Digi-Key

10 $0.24 .050" jumper short S9345-ND Digi-Key

1 $0.86 .5mm 4-pos FFC connector OR746CT-ND Digi-Key

1 $2.34 1mm 20-pos FFC connector WM7964CT-ND Digi-Key

10 $0.02 1.2Kohm resistor P1.2KGCT-ND Digi-Key

10 $0.05 .1uF 10V 399-1095-1-ND 0603 Digi-Key

5 $0.02 1ea 47Kohm resistor P47KGCT-ND 0603 Digi-Key

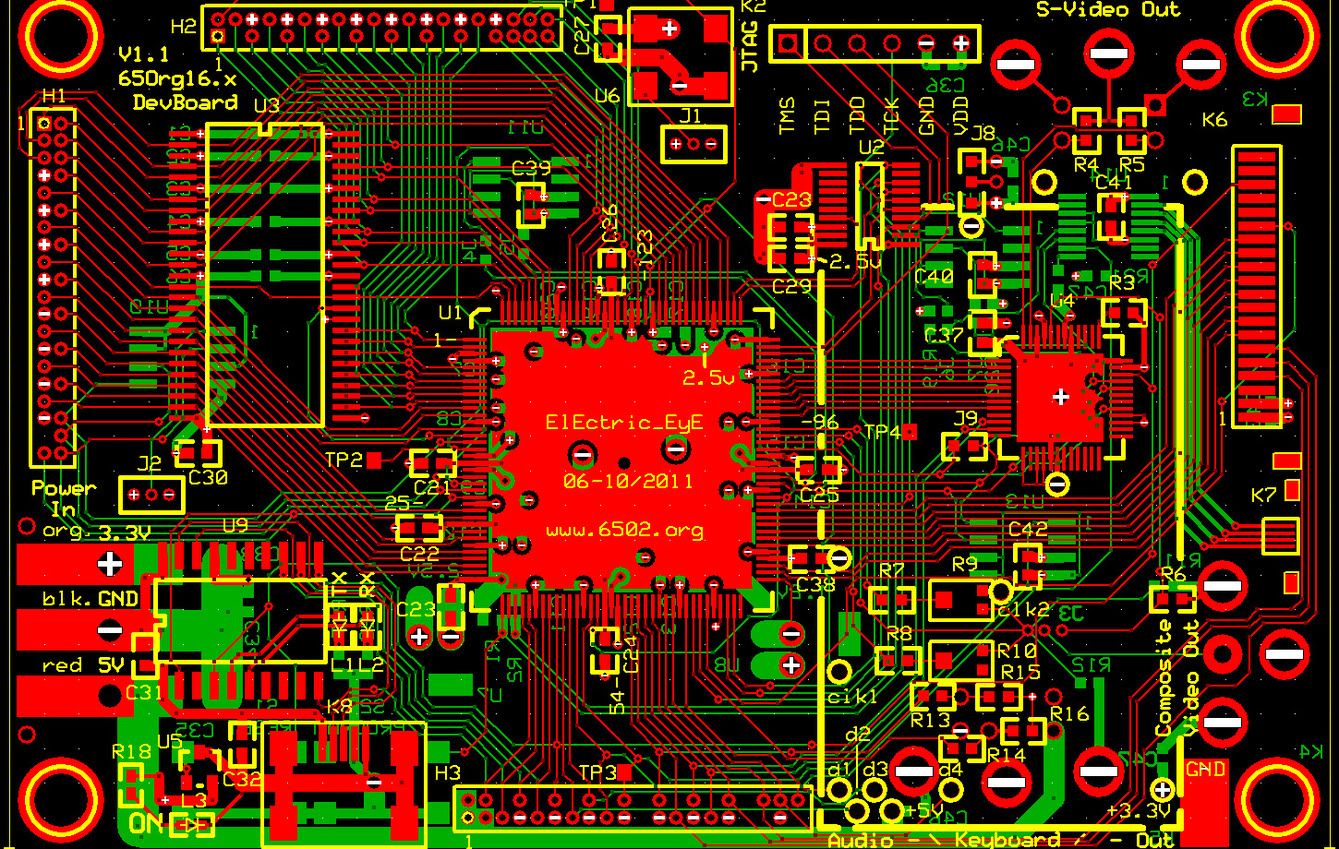

Here is the V1.1 DevBoard Layout:

Here is the V1.1 DevBoard

Schematic.

Here is the

pinout for the expansion Headers.

EDIT (12/17/2011): Added parts list per request. Initial post, incomplete...

EDIT (1/7/2012): Added Memory Map

EDIT (1/17/2012): Added Random Number Generator to Memory Map.

EDIT (1/20/2012): Added Board Layout and Schematic.

EDIT (3/27/2012): Added updated Header info. NOTE: Header pinouts are not up to date on Schematic.