Experimental TTL implementation of the 6522

Posted: Mon Mar 04, 2019 4:42 pm

For supporting a project which aims at building a TTL implementation of the 6526,

I dug out my old schematics for an experimental 6522 TTL implementation, the X22.

Because the most recent version of Eagle can't open Eagle 3.55 files anymore, I converted them to *.png.

Edit:

The thread became a bit longer than expected, also featuring:

6521, 6523, 6532, 6545, 6551\6850.

;---

The design was experimental and partially untested,

I'm not sure if the timers were cycle exact,

and if you try to make use of these echematics,

please take them with a grain of salt and try to build things a bit different from them.

It seemed to have worked with a Rockwell R65C02-2 running at 4MHz.

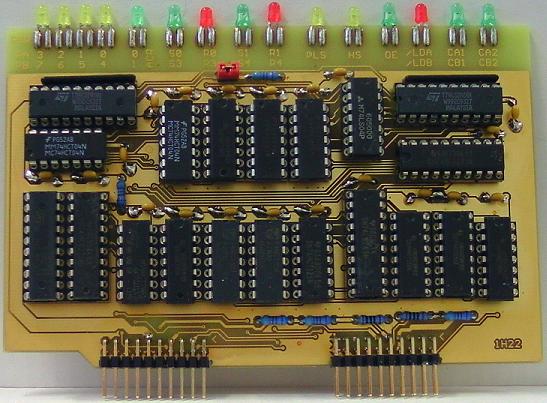

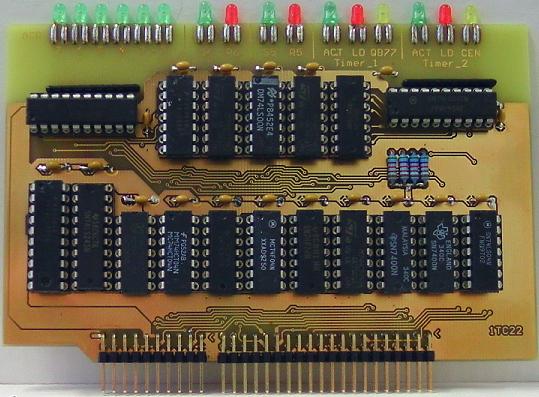

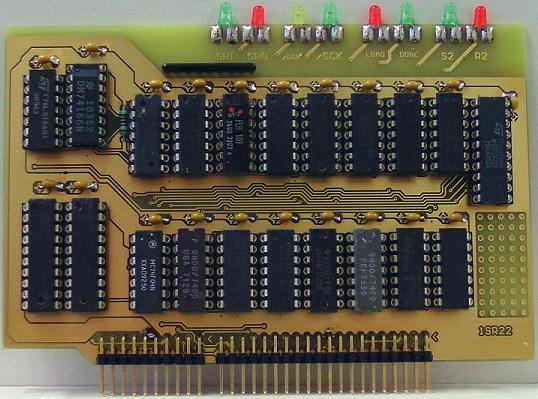

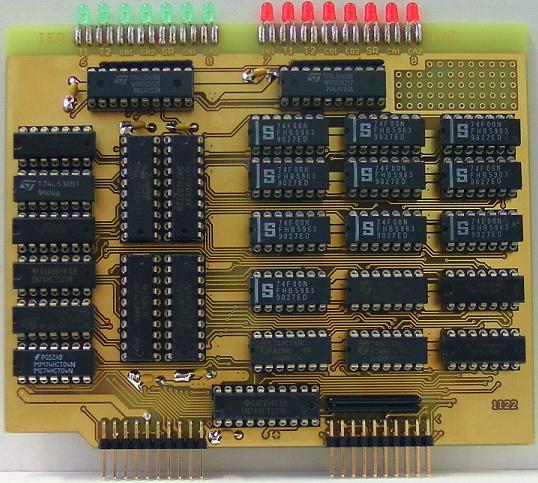

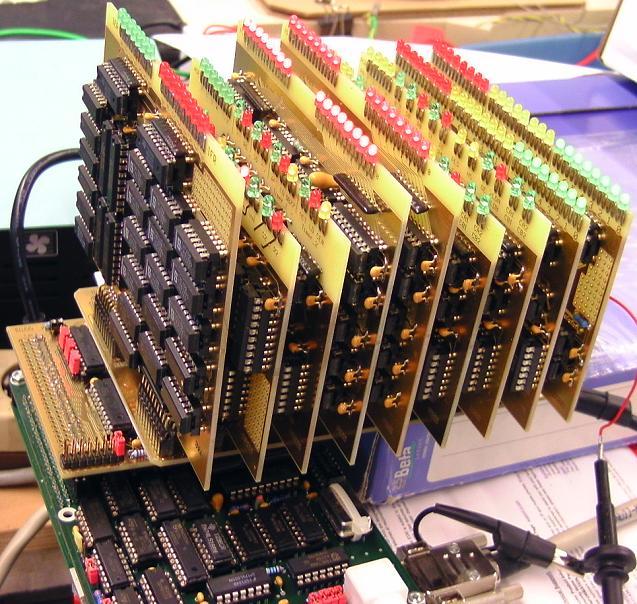

Test setup:

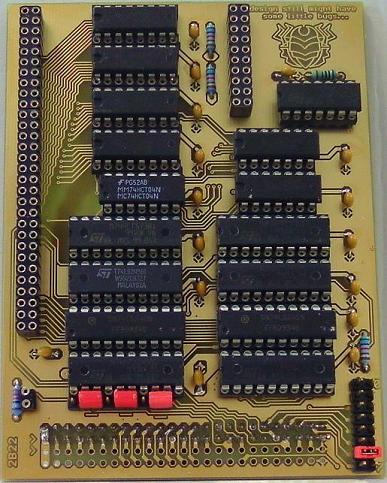

Bottom: my DRC2 SBC, which is supposed to be compatible to the SBC-2.

2B22 bus interface is plugged into DRC2.

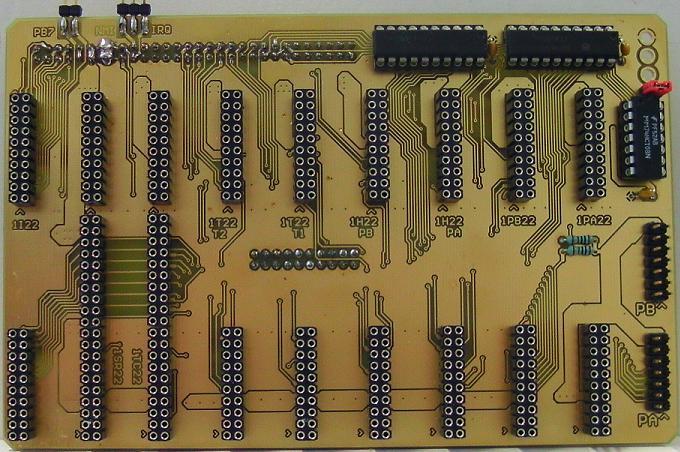

X22 backplane is plugged into the 2B22 bus interface.

Plugged into the X22 backplane, we have:

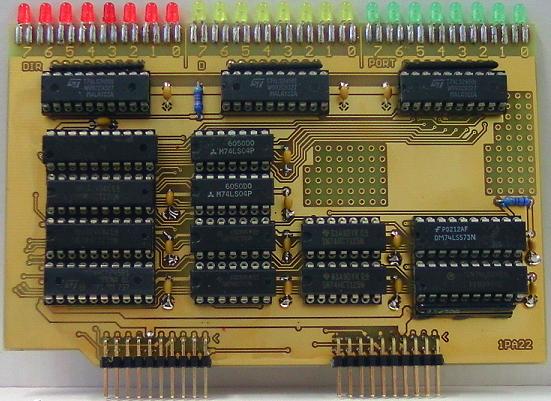

1* 1PA22, Port A module

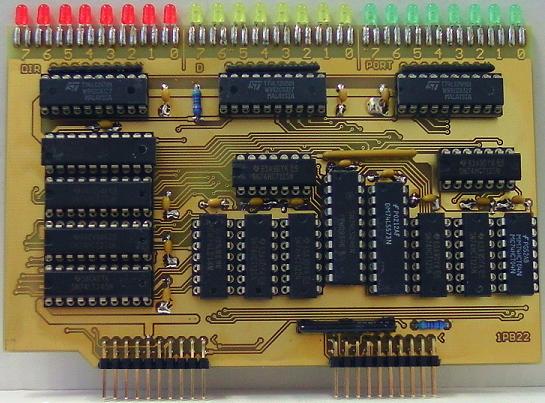

1* 1PB22, Port B module

2* 1H22, handshake module

2* 1T22, timer module

1* 1TC22, timer control module

1* 1SR22, shift register module

1* 1I22, interrupt module

I dug out my old schematics for an experimental 6522 TTL implementation, the X22.

Because the most recent version of Eagle can't open Eagle 3.55 files anymore, I converted them to *.png.

Edit:

The thread became a bit longer than expected, also featuring:

6521, 6523, 6532, 6545, 6551\6850.

;---

The design was experimental and partially untested,

I'm not sure if the timers were cycle exact,

and if you try to make use of these echematics,

please take them with a grain of salt and try to build things a bit different from them.

It seemed to have worked with a Rockwell R65C02-2 running at 4MHz.

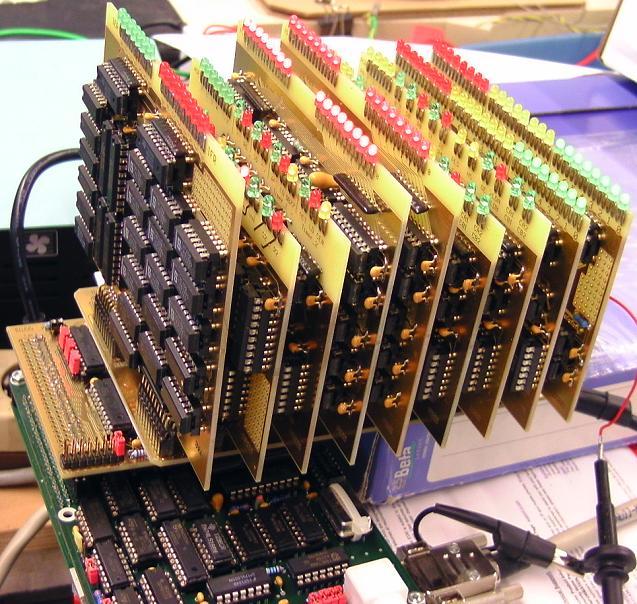

Test setup:

Bottom: my DRC2 SBC, which is supposed to be compatible to the SBC-2.

2B22 bus interface is plugged into DRC2.

X22 backplane is plugged into the 2B22 bus interface.

Plugged into the X22 backplane, we have:

1* 1PA22, Port A module

1* 1PB22, Port B module

2* 1H22, handshake module

2* 1T22, timer module

1* 1TC22, timer control module

1* 1SR22, shift register module

1* 1I22, interrupt module