Page 1 of 2

How did MOS design and photomask technology evolve?

Posted: Fri Dec 29, 2017 10:35 am

by kakemoms

Hi

I am trying to find out more about how the different revisions of the original MOS6560 (VIC) chip was manufactured. It was designed in 1975-1977, so I guess it started out with hand layout on paper and Rubylith(like the 6502), but by the last batch (1984) it must have gone through some transitions. Was it digitized? Translated into VHDL? If anyone here knows anything about how MOS design and photomask manufacturing changed in the 1977-1983 period, I would like to hear about it.

Re: How did MOS design and photomask technology evolve?

Posted: Fri Dec 29, 2017 7:23 pm

by White Flame

MOS was ahead of the curve as far as tricks for increasing yield and using computerized layout tools. I'm sure that their tools got smarter approaching '84, though my guess would be evolutionary development process advancement and not necessarily switching to VHDL. That's about as far as my knowledge goes.

Re: How did MOS design and photomask technology evolve?

Posted: Sat Jan 06, 2018 5:28 pm

by kakemoms

I was actually able to find out several things from this old factory tour video:

https://m.youtube.com/watch?v=xu8Fi0tC9IA

Its from around 1982-1983 and we can see some really large terminals, grapical layout and big paper plots. No vhdl there. Its also possible to see that the engineer works on a "7520" which never reached the market.. The cleanroom shots with yellow light shows several steppers and we are also shown a reticle (used in projection aligners).

A nice factory, quite up to date, but unfortunately everything made on 4inc which in the long run was an expensive process (especially for the larger Amiga chips). Equipment cost for going to smaller transistors were also increasing exponentially, which would have needed a considerable investment by around 1986-1987. I don't know if that factory ever got to 6 inc, or was just closed down by that time.

Re: How did MOS design and photomask technology evolve?

Posted: Sat Jan 06, 2018 6:17 pm

by BigEd

That fits my experience. In the mid-80s we were using Calma 2 workstations, where you could directly enter and edit layout, and there was at least one remaining Calma 1 unit, which I think was more about digitising from drawings - there was still a rank of giant drafting boards.

We did describe our designs in a simulation language so we could do logic simulation, but there was no direct link to layout - no synthesis. When I first used synthesis technology, probably in the early 90s, the software was already very expensive, and it only got more expensive as time went on. (There was some logic minimisation software from the academic world which was free, and that helped if you had a PLA or similar regular logic implementation.)

Re: How did MOS design and photomask technology evolve?

Posted: Thu Oct 04, 2018 4:06 am

by kakemoms

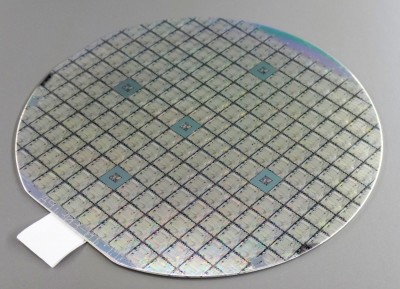

Well, just to follow this up a little bit. I recently bought a 6569R5 wafer from someone on ebay. It is a full 4 inc/100 mm (pick your choice) wafer with 6569R5 chips. I am not sure if some of them are marked (bad ones), so this may have came out from before device testing. There is also 5 smaller chips on it, which are probably a test run of some other component. It looks like it has been decently stored.

The 4 inc wafer is the reason Commodore made very little money. Compared to 6 inc process, 4 inc was much more expensive per chip to run. A contemporary report from Intel shows this really well. Looking at the wafer we can see that its only about 250 chips on them as the 6569 is quite large.

I also include some other wafer pictures from MOS. All made in 1984 or later on 4 inc. In fact, one (dma controller) seems to be an Amiga component used in the A2090 scsi controller which was sold from 1988.

All-in-all this seems to indicate that Commodore stuck to their 4 inc process into the late 1988. Not surprising since they had little money at the time, and it looks like they neither put capital aside to replace the fading 4 inc process.

MOS 6569R5 VIC-II:

- MOS 6569R5 VIC-II

MOS 6525R3 TRI-PORT interface (confirmed by seller that this is not the 6526, but the 6525):

MOS 8721R3 PLA

MOS 8727R3 DMA

Re: How did MOS design and photomask technology evolve?

Posted: Thu Oct 04, 2018 10:47 am

by Tor

Well, just to follow this up a little bit. I recently bought a 6569R5 wafer from someone on ebay. It is a full 4 inc/100 mm (pick your choice) wafer with 6569R5 chips.

O-K... we've already had encouraging posts about how to do the tricky tiny surface mount soldering.. I've even tried following the instructions myself (although with less success than I hoped). So now we're looking forward to future posts about how to solder up your wafer chips!

Definitely a step up in complexity I suspect.

Re: How did MOS design and photomask technology evolve?

Posted: Thu Oct 04, 2018 1:06 pm

by BigEd

Nice! The pads will be scratched if the chips have been tested - probe cards leave marks. But I don't see any ink spots, so probably not.

My feeling is that 6inch wafers came quite late in the day. And of course, did not arrive everywhere at once. And indeed, the capital cost of a new line with all new equipment is enormous - not only do you need to find the money, but you need to be the kind of outfit with an eye to the future returns on that investment. And, to keep a 6 inch fab busy, you need to make a huge number of chips. Probably Commodore were too small volume to do that.

Re: How did MOS design and photomask technology evolve?

Posted: Thu Oct 04, 2018 5:55 pm

by GARTHWILSON

In 1984-85 (two jobs ago), I worked at a company that made VHF and UHF power transistors, mostly for military radars and communications, although they also made cable-TV amplifiers. Their wafers at that time were all 3".

Re: How did MOS design and photomask technology evolve?

Posted: Fri Oct 05, 2018 1:48 am

by kakemoms

Well, just to follow this up a little bit. I recently bought a 6569R5 wafer from someone on ebay. It is a full 4 inc/100 mm (pick your choice) wafer with 6569R5 chips.

O-K... we've already had encouraging posts about how to do the tricky tiny surface mount soldering.. I've even tried following the instructions myself (although with less success than I hoped). So now we're looking forward to future posts about how to solder up your wafer chips!

Definitely a step up in complexity I suspect.

Haha.. well, I could actually do that as I have access to alot of equipment. Including Silicon dicing saw, wirebonders (the thing that attach gold wires to the edge of the chip) ++. Finding the time and need is another matter, and you can still buy 6569 from ebay.. so why destroy an important piece of history for that.

So no, I am actually going to keep it as a wafer. My only regret is not finding earlier 6560 or 6561 wafers. Or even a 6566.

Re: How did MOS design and photomask technology evolve?

Posted: Fri Oct 05, 2018 2:08 am

by kakemoms

Nice! The pads will be scratched if the chips have been tested - probe cards leave marks. But I don't see any ink spots, so probably not.

My feeling is that 6inch wafers came quite late in the day. And of course, did not arrive everywhere at once. And indeed, the capital cost of a new line with all new equipment is enormous - not only do you need to find the money, but you need to be the kind of outfit with an eye to the future returns on that investment. And, to keep a 6 inch fab busy, you need to make a huge number of chips. Probably Commodore were too small volume to do that.

Well, Intel and TI survived that way.. and they also made chips for others. I guess the ultimate reason was Commodore's owner Gould. He has been described as one that didn't want to loose control of the company, so he would probably not have allow such a huge capital raise... But it remains speculation.

This report though is no speculation:

https://www.chiphistory.org/chc_upload/ ... erview.pdf

With MOS, Commodore had a large edge over competitors in the early 80'ies. They could force price much lower without loosing money. With Amiga's many custom chips, they had the same edge even without the 68000 cpus. But with a costly 4inc line not being upgraded, that edge would have ultimately gone.. and they eventually bled out.

Another interesting thing (from the other pictures) are the ink spots. The 6525 for example, has a huge number of failed chips. Way lower than the 99.9% required for efficient production. Its slightly amusing, but also a sad fact.

You can argue that many of their products in the 90'ies were flops.. but such things are often decided by pricing. I remember the CD32 being way ahead of its time with videos on CD's.. but it was too expensive.

Edit: The 6526 "TRIPORT interface" was indeed the 6525 TRIPORT interface, not the 6526 PIA. I've bought one of those as well. I will try to examine it under an electron microscope when I get the chance (probably in around 4 weeks).

Re: How did MOS design and photomask technology evolve?

Posted: Fri Oct 05, 2018 8:07 am

by BigEd

Nice PDF, thanks! There's a table on page 47 which illustrates the difficulty of justifying a new fab, and a quote that the industry found the transition to 5" wafers "quite difficult" - even in 1989 we see 6" wafers are in the future (oops, no, I misread), and the extrapolated costs are enormous. Also notable in the article, the semiconductor industry ships $66billion of product, of which $40million is in the consumer sector. We see that a company like Commodore is an absolute minnow, and it's an unlikely circumstance, an accident of their history, that they find themselves with a fab of their own at all.

(Earliest) introduction date of each wafer size:

1965 1¼ inch

1974 4 inch

1979 5 inch

1985 6 inch

1987 8 inch

Bill Mensch

recollects that Moto, and then MOS, were not yet using 4 inch wafers at the time of the 6502 introduction, and that MOS were getting 100 good die per wafer compared to Moto's 10. (I'd take this with a grain of salt, personally, but I'm sure there's some truth in it.)

Re: How did MOS design and photomask technology evolve?

Posted: Fri Oct 05, 2018 8:39 am

by Konrad_B

Well, just to follow this up a little bit. I recently bought a 6569R5 wafer from someone on ebay.

This reminds me of the (ex) GMT/MOS office cleanup done last year - some wafers were found there, as well as lots of backup tapes and some rotten Pets (C65s were scrapped at the beginning of the cleanup) etc.

https://imgur.com/a/KhlIr

Now the question is - who took the tapes, as scrapping them would be an unbelievable loss...

Re: How did MOS design and photomask technology evolve?

Posted: Sun Oct 07, 2018 1:30 am

by dwight

I doubt you could solder to the dies even if you had something that could do that. The pads look to be aluminum. I know there are aluminum solders but most of them would dissolve the pads in a micro second.

Wires, aluminum or gold, were put down with sonic welders, not soldered.

Dwight

Re: How did MOS design and photomask technology evolve?

Posted: Sun Oct 07, 2018 7:38 am

by BigEd

Jut a thought, for a hobbyist, would the tiniest drop of silver epoxy serve to connect the thinnest wire to a bond pad? You'd need a microscope and a micromanipulator, I'd think.

Re: How did MOS design and photomask technology evolve?

Posted: Mon Oct 08, 2018 5:11 am

by dwight

It might be easier to make a sonic welder. I suspect the Piezo bars used in some of the lap tops to create the high voltage for the display lighting tubes, could be used. It doesn't need to much ultasonic.

Dwight