Proof reading memory map

Posted: Mon Oct 12, 2015 4:49 am

Hello! If you guys could help me go through my memory decoding scheme to make sure I haven't done anything wrong that would be greatly appreciated :D

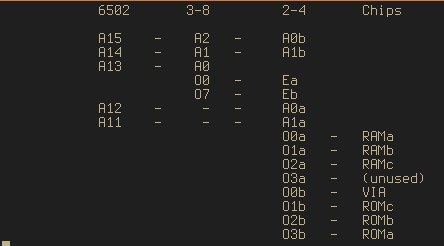

Chips:

3 - 2k ROM

3 - 2k RAM

1 - 6522 VIA

1 - 74LS139 2 to 4 decoder (two on the dip)

1 - 74LS138 3 to 8 decoder

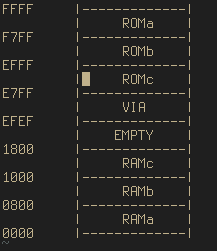

Goal is to divide the address space in 8 chunks of 8k, and the first and last chunks into 4 2k each. The 3-8 decoder will enable the adequate side of the 2-4 decoder through it's enable lines (here marked Ea and Eb) which will

then enable the appropriate chip.

Intended memory map:

Sorry if I'm a little too hard to understand, this is my first attempt at this.

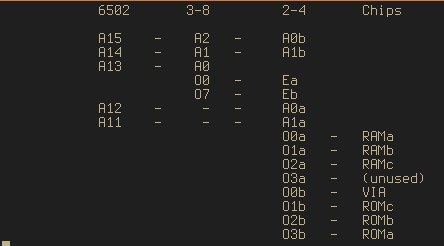

Chips:

3 - 2k ROM

3 - 2k RAM

1 - 6522 VIA

1 - 74LS139 2 to 4 decoder (two on the dip)

1 - 74LS138 3 to 8 decoder

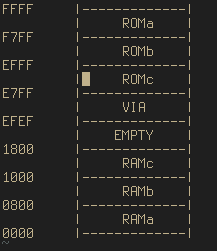

Goal is to divide the address space in 8 chunks of 8k, and the first and last chunks into 4 2k each. The 3-8 decoder will enable the adequate side of the 2-4 decoder through it's enable lines (here marked Ea and Eb) which will

then enable the appropriate chip.

Intended memory map:

Sorry if I'm a little too hard to understand, this is my first attempt at this.